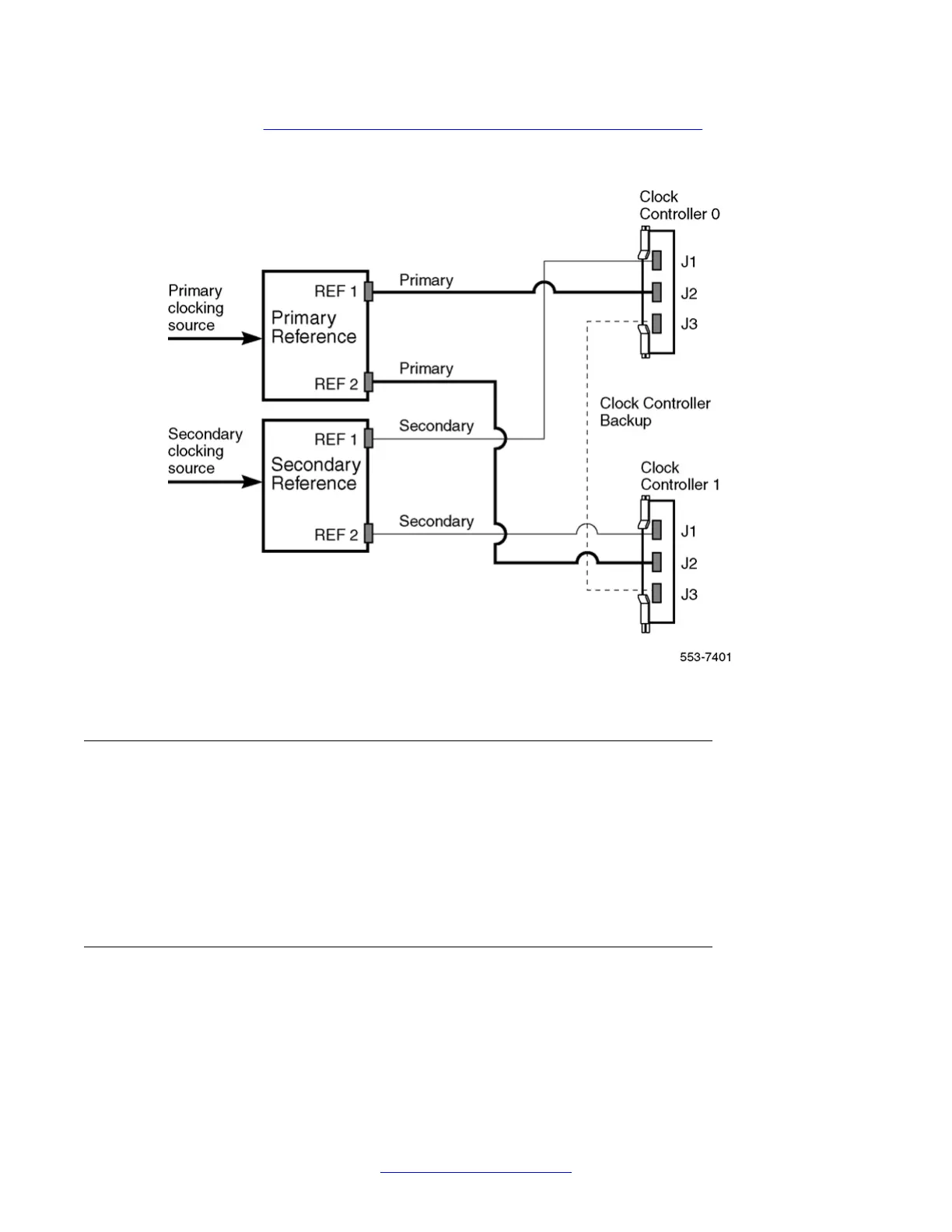

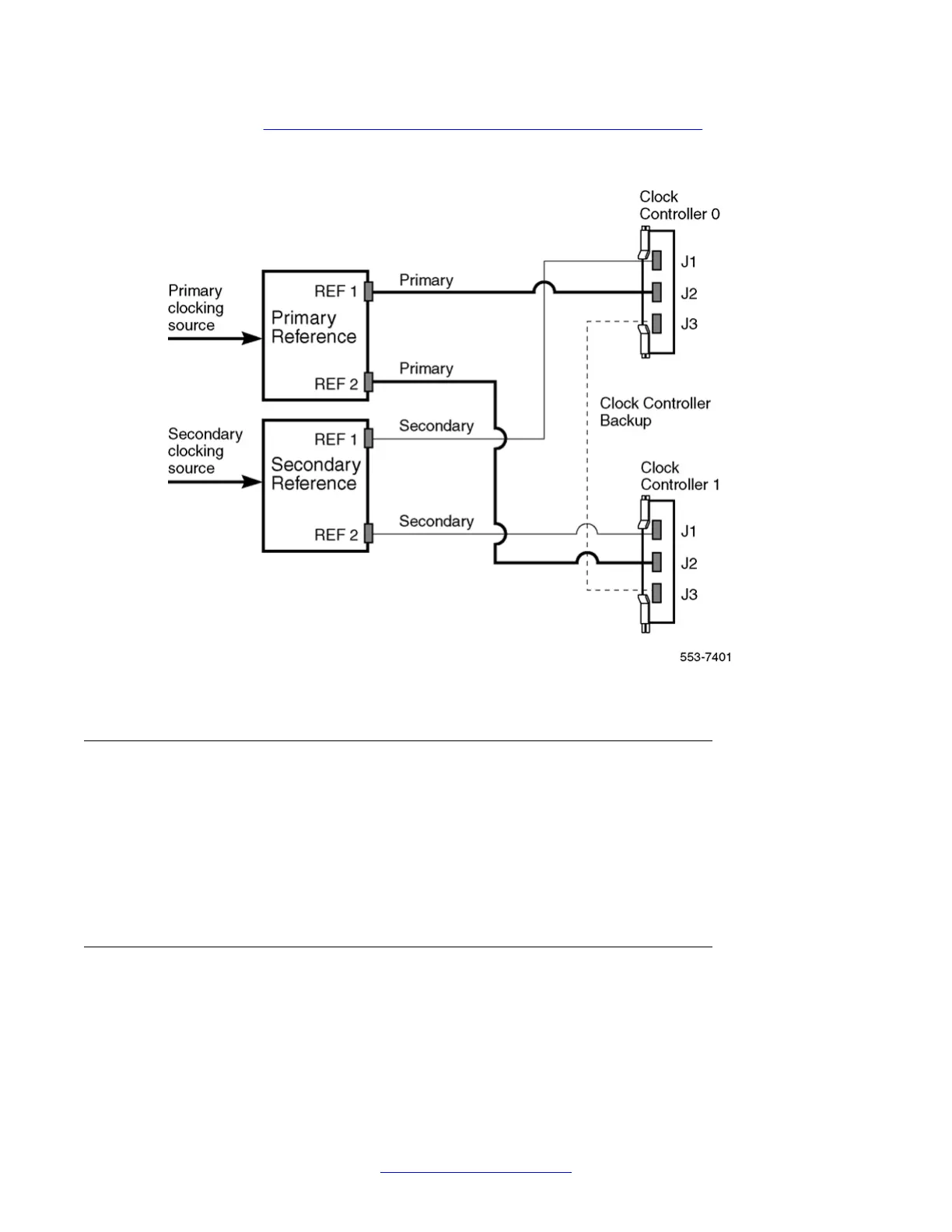

As shown in Figure 14: Clock controller primary and secondary tracking on page 78, a system

with a dual CPU can have two clock controllers (CC0 and CC1). One clock controller acts as

a backup to the other. The clock controllers should be locked to the reference clock.

Figure 14: Clock controller primary and secondary tracking

Free run (non-tracking) mode

The clock synchronization for a PRI loop can operate in free-run mode if

•

the loop is not defined as the primary or secondary clock reference

• the primary and secondary references are disabled

• the primary and secondary references are in local alarm

Reference clock errors

System software checks every 0-15 minutes (programmable) to see if a clock-controller or

reference-clock error has occurred.

Clock controller maintenance

78 ISDN Primary Rate Interface Maintenance November 2011

Comments? infodev@avaya.com

Loading...

Loading...