AW00089317000 Standard Features

Basler ace GigE 211

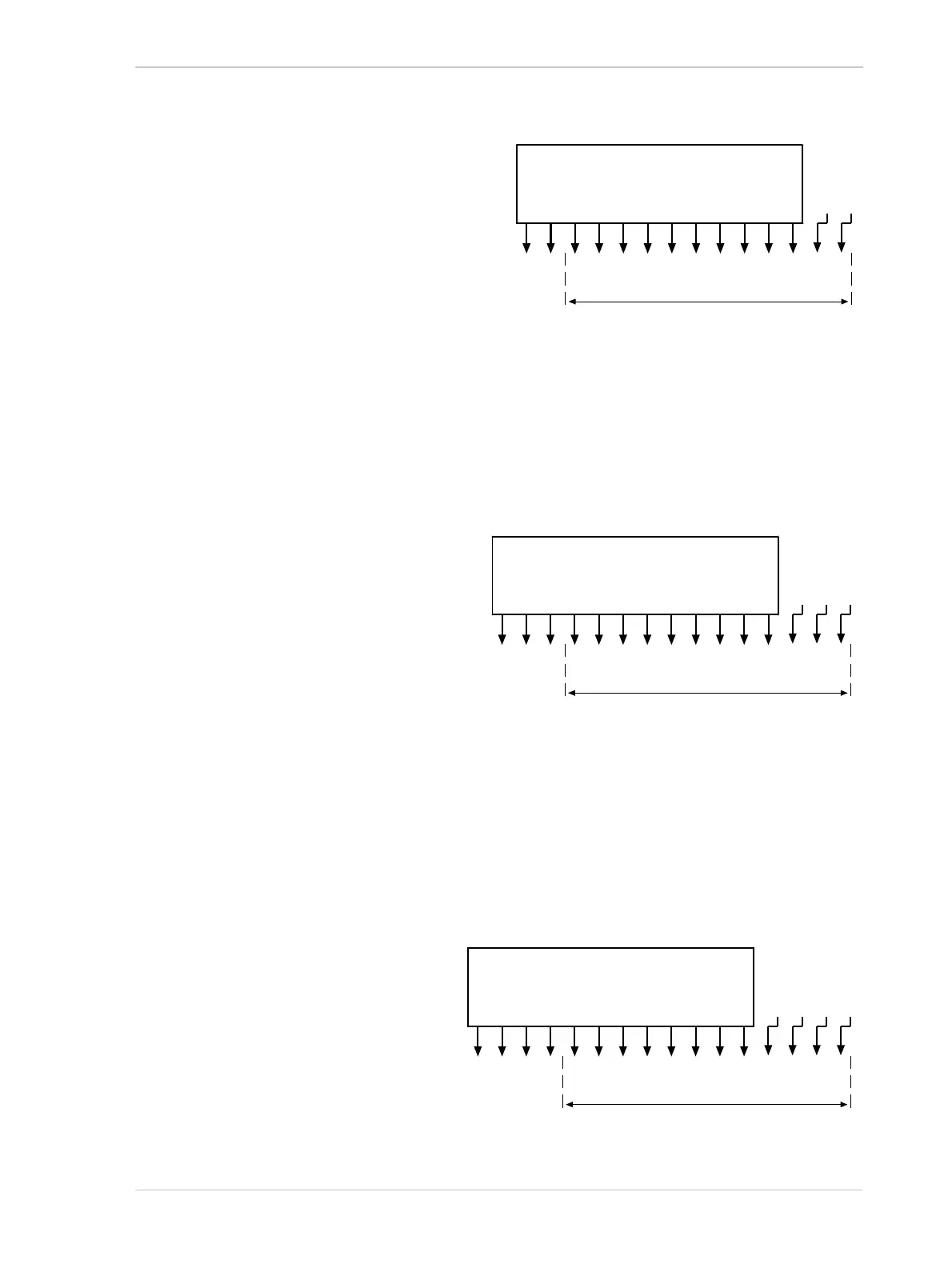

Shift by 2

When the camera is set to shift by 2, the output

from the camera will include bit 9 through bit 0

from the ADC along with 2 zeros as LSBs.

The result of shifting twice is that the output of

the camera is effectively multiplied by 4.

When the camera is set to shift by 2, the 2 least

significant bits output from the camera for each

pixel value will be 0. This means that the gray

value scale will only include every 4th value, for

example, 4, 8, 16, 20, and so on.

If the pixel values being output by the camera’s sensor are high enough to set bit 10 or bit 11 to 1,

we recommend not using shift by 2. If you do nonetheless, all bits output from the camera will

automatically be set to 1. Therefore, you should only use the shift by 2 setting when your pixel

readings with a 12 bit pixel format selected and with digital shift disabled are all less than 1024.

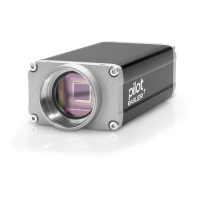

Shift By 3

When the camera is set to shift by 3, the

output from the camera will include bit 8

through bit 0 from the ADC along with 3

zeros as LSBs.

The result of shifting 3 times is that the

output of the camera is effectively multiplied

by 8.

When the camera is set to shift by 3, the 3

least significant bits output from the camera

for each pixel value will be 0. This means that the gray value scale will only include every 8th gray

value, for example, 8, 16, 24, 32, and so on.

If the pixel values being output by the camera’s sensor are high enough to set bit 9, bit 10, or bit 11

to 1, we recommend not using shift by 3. If you do nonetheless, all bits output from the camera will

automatically be set to 1. Therefore, you should only use the shift by 3 setting when your pixel

readings with a 12 bit pixel format selected and with digital shift disabled are all less than 512.

Shift By 4

When the camera is set to shift by 4, the

output from the camera will include bit 7

through bit 0 from the ADC along with 4

zeros as LSBs.

The result of shifting 4 times is that the

output of the camera is effectively

multiplied by 16.

ADC

Shifted Twice

M

S

B

L

S

B

bit

0

bit

1

bit

2

bit

3

bit

4

bit

5

bit

6

bit

7

bit

8

bit

9

bit

10

bit

11

"0" "0"

ADC

Shifted Three Times

M

S

B

L

S

B

bit

0

bit

1

bit

2

bit

3

bit

4

bit

5

bit

6

bit

7

bit

8

bit

9

bit

10

bit

11

"0" "0" "0"

ADC

Shifted Four Times

M

S

B

L

S

B

bit

0

bit

1

bit

2

bit

3

bit

4

bit

5

bit

6

bit

7

bit

8

bit

9

bit

10

bit

11

"0" "0" "0" "0"

Loading...

Loading...