458

CHAPTER 19 SERIAL INTERFACE CHANNEL 2

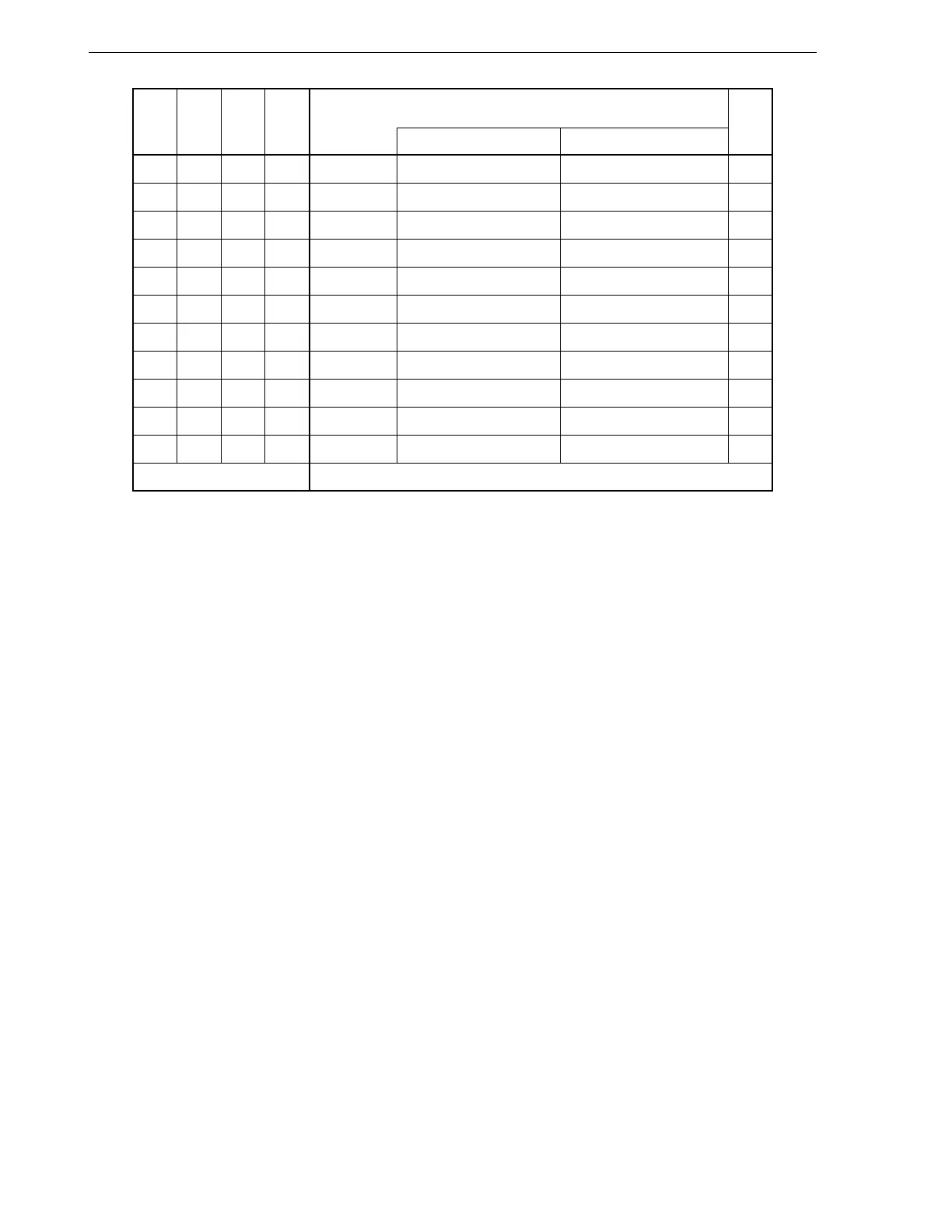

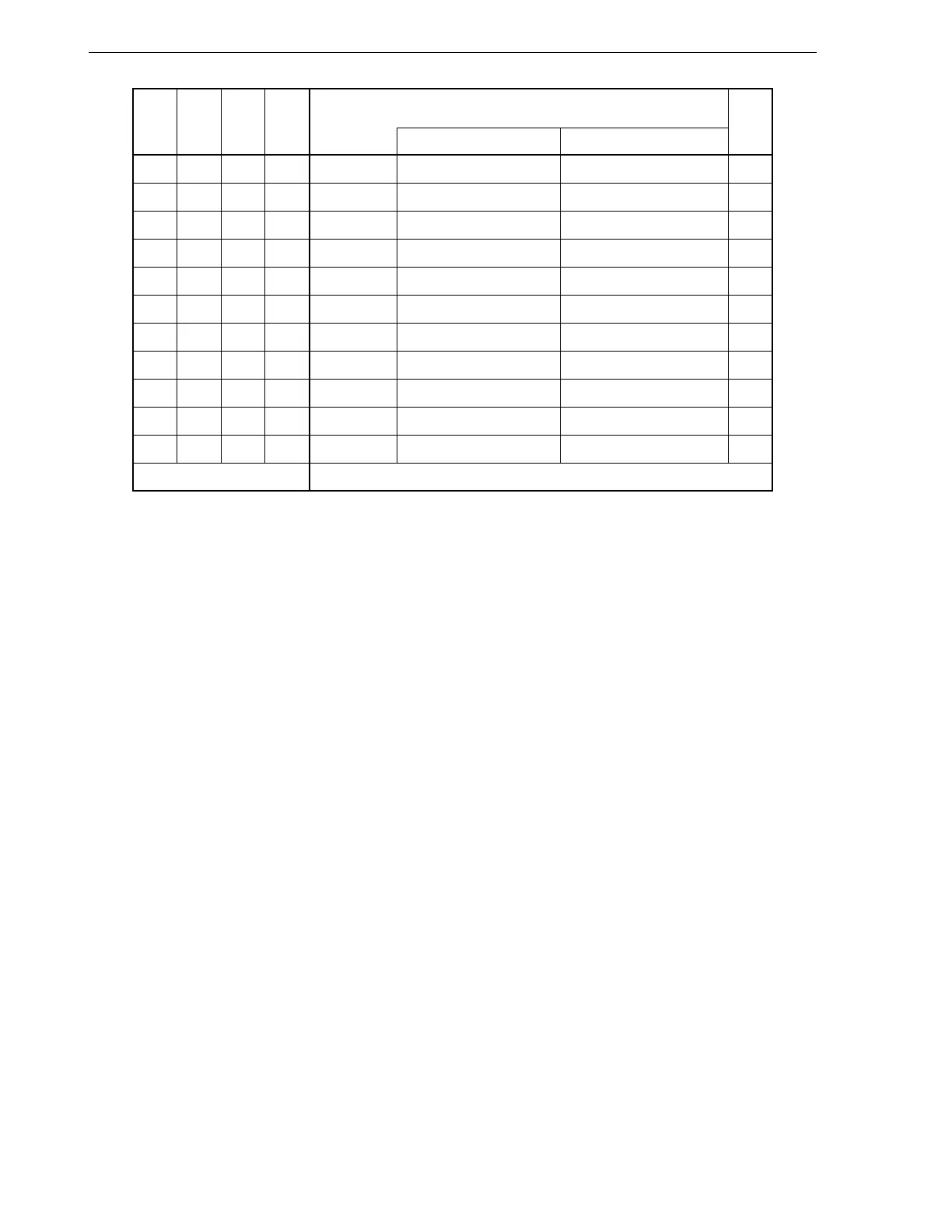

5-Bit Counter Source Clock Selection

TPS3 TPS2 TPS1 TPS0 n

MCS = 1 MCS = 0

0000fXX/2

10

fX/2

10

(4.9 kHz) fX/2

11

(2.4 kHz) 11

0101fXX fX (5.0 MHz) fX/2 (2.5 MHz) 1

0110fXX/2 fX/2 (2.5 MHz) fX/2

2

(1.25 MHz) 2

0111fXX/2

2

fX/2

2

(1.25 MHz) fX/2

3

(625 kHz) 3

1000fXX/2

3

fX/2

3

(625 kHz) fX/2

4

(313 kHz) 4

1001fXX/2

4

fX/2

4

(313 kHz) fX/2

5

(156 kHz) 5

1010fXX/2

5

fX/2

5

(156 kHz) fX/2

6

(78.1 kHz) 6

1011fXX/2

6

fX/2

6

(78.1 kHz) fX/2

7

(39.1 kHz) 7

1100fXX/2

7

fX/2

7

(39.1 kHz) fX/2

8

(19.5 kHz) 8

1101fXX/2

8

fX/2

8

(19.5 kHz) fX/2

9

(9.8 kHz) 9

1110fXX/2

9

fX/2

9

(9.8 kHz) fX/2

10

(4.9 kHz) 10

Other than above Setting prohibited

Caution When a data is written to BRGC during a communication operation, baud rate generator

output is disrupted and communication cannot be performed normally. Therefore, data

must not be written to BRGC during a communication operation.

Remarks 1. f

X : Main system clock oscillation frequency

2. fXX : Main system clock frequency (fX or fX/2)

3. MCS : Oscillation mode selection register (OSMS) bit 0

4. n : Value set in TPS0 to TPS3 (1 ≤ n ≤ 11)

5. Figures in parentheses apply to operation with f

X = 5.0 MHz.

Loading...

Loading...