RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1294

Dec 10, 2015

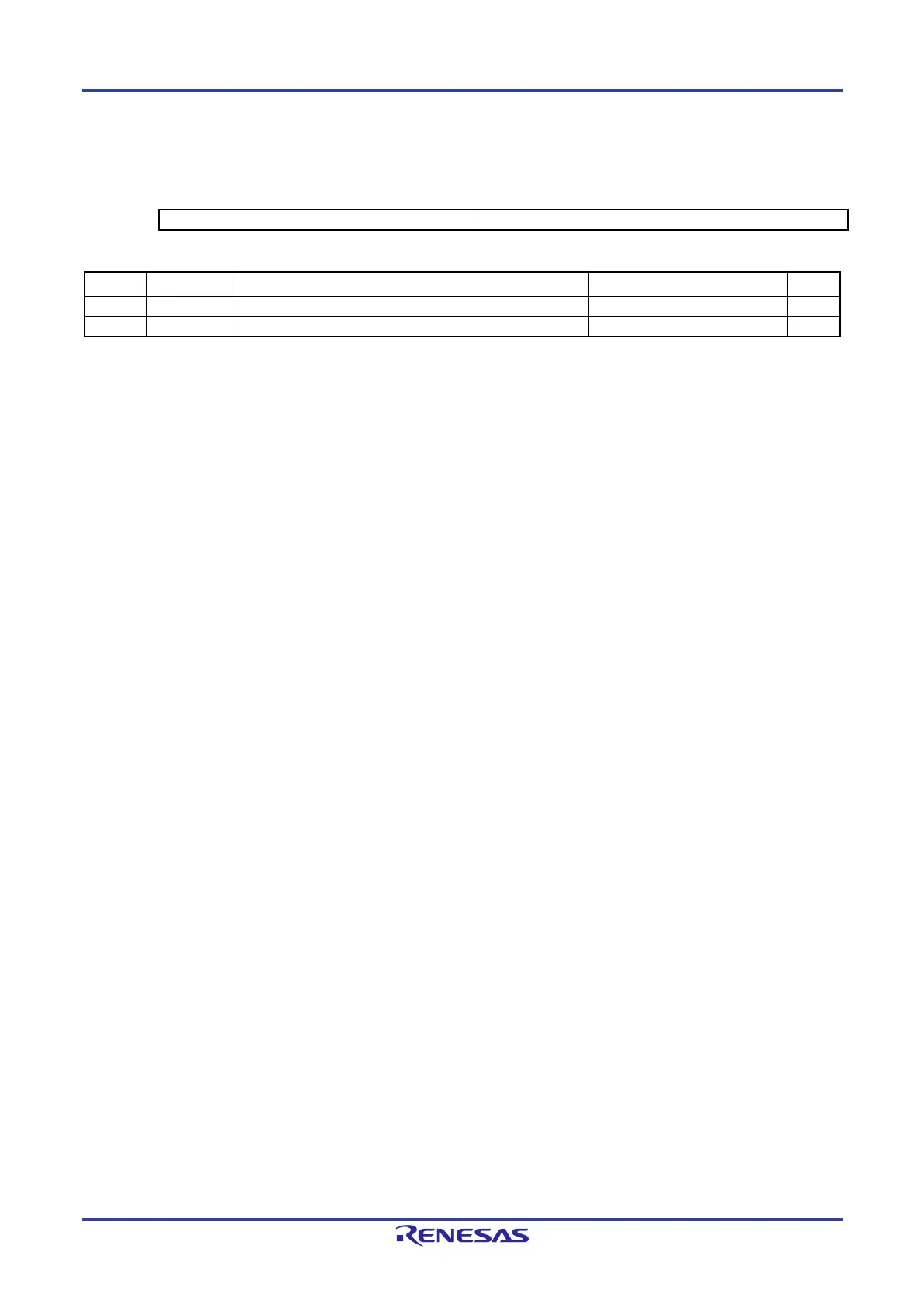

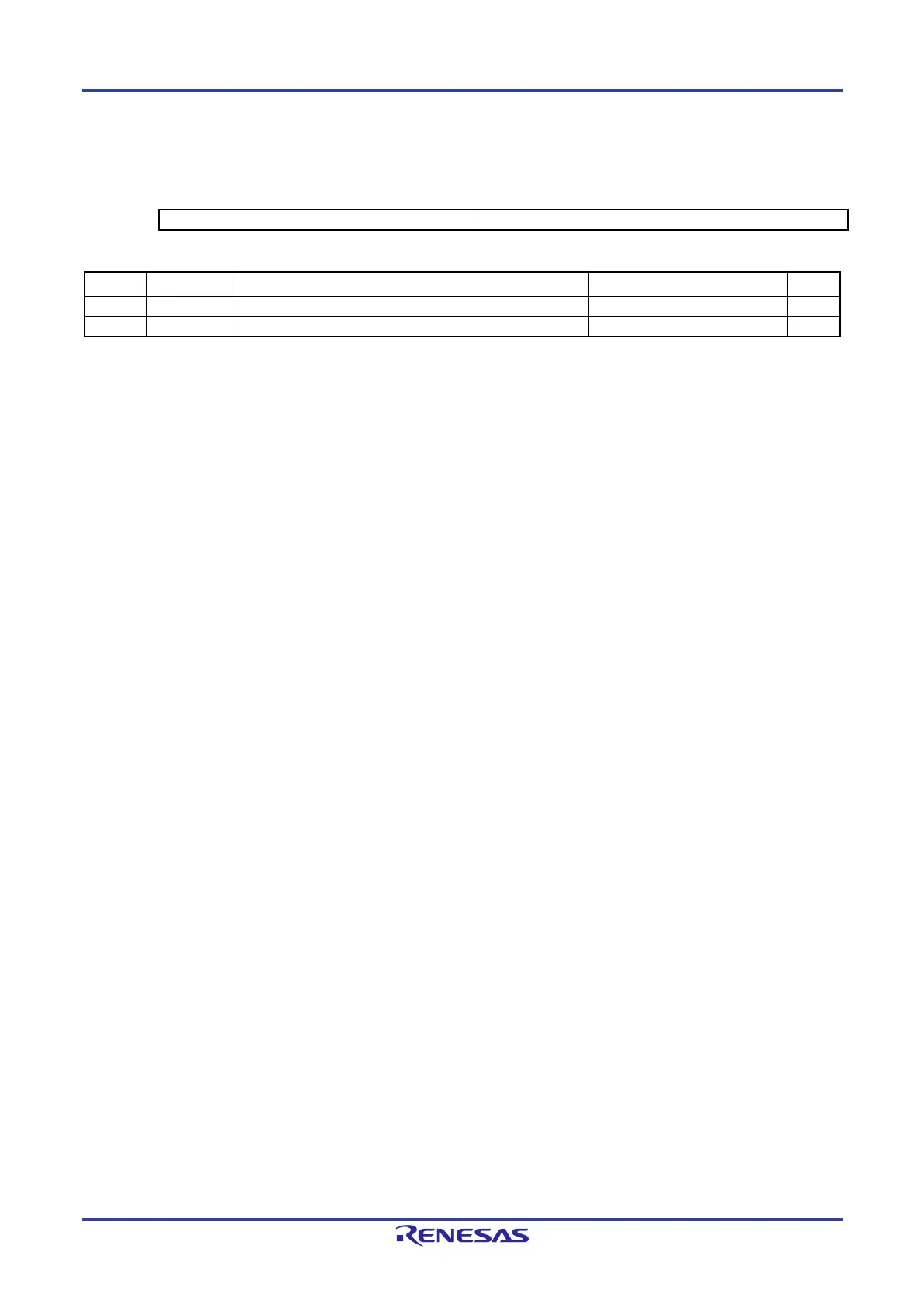

18.3.6 CANi Status Register H (CiSTSH) (i = 0)

Address C0STSHL: F030AH, C0STSHH: F030BH

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

TEC[7:0] REC[7:0]

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit Symbol Description Counter Value R/W

15 to 8 TEC[7:0] The transmit error counter (TEC) can be read. — R

7 to 0 REC[7:0] The receive error counter (REC) can be read. — R

• TEC[7:0] Bits

These bits indicate the transmit error counter value. For transmit error counter increment/decrement conditions,

see the CAN specifications (ISO11898-1).

These bits are cleared to 0 in channel reset mode.

• REC[7:0] Bits

These bits indicate the receive error counter value. For receive error counter increment/decrement conditions,

see the CAN specifications (ISO11898-1).

These bits are cleared to 0 in channel reset mode.

Loading...

Loading...