RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1299

Dec 10, 2015

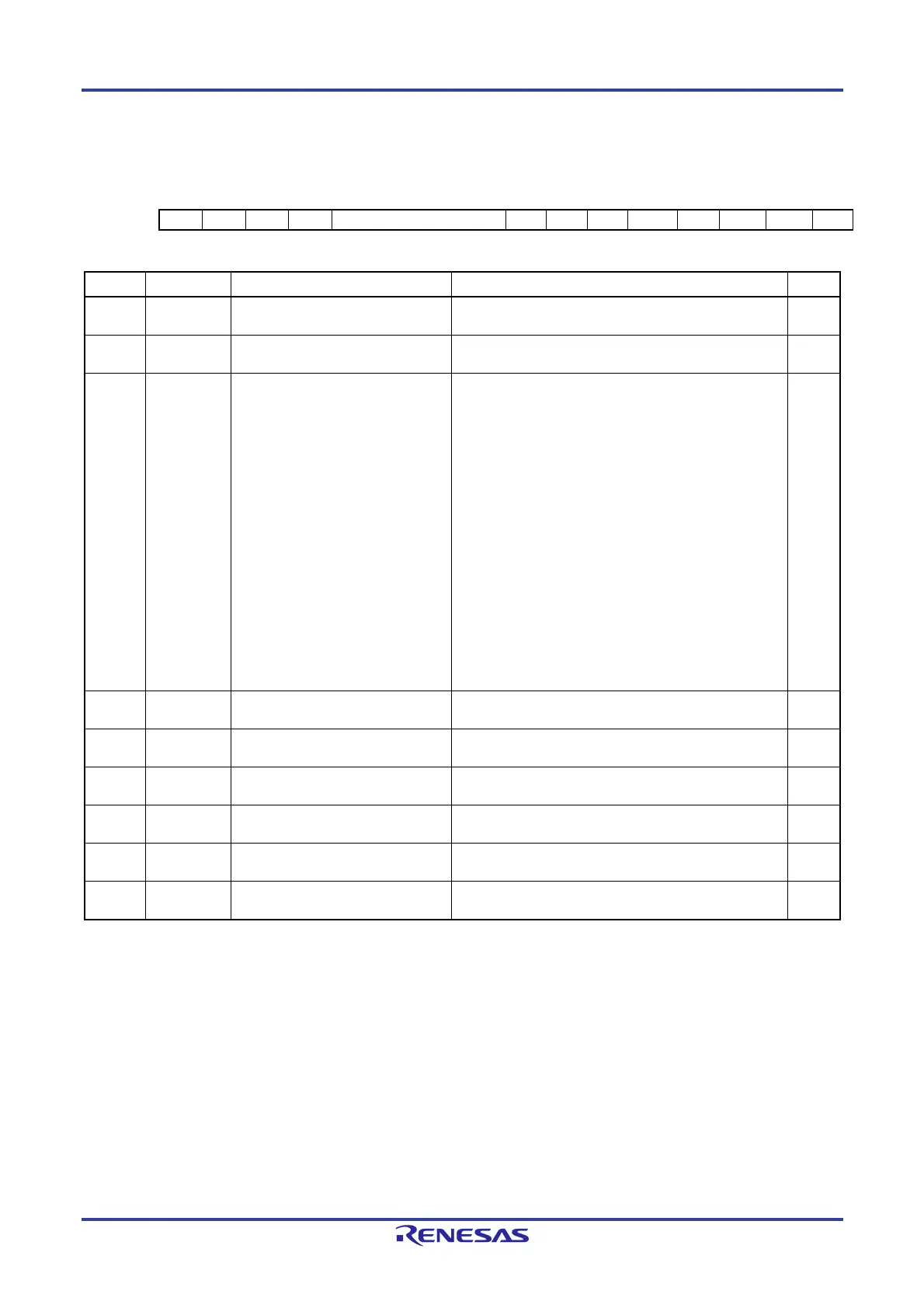

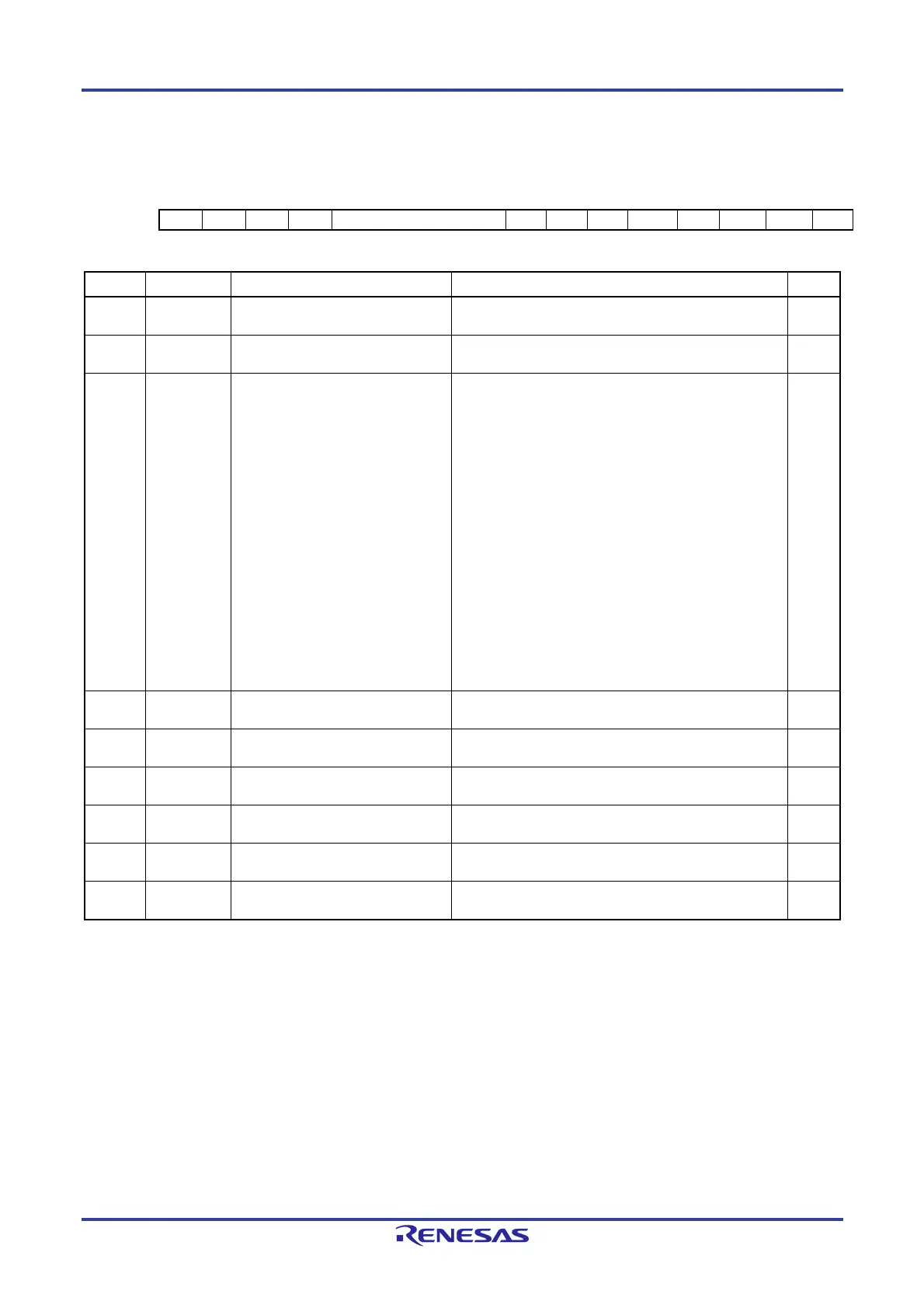

18.3.9 CAN Global Configuration Register L (GCFGL)

Address GCFGLL: F0322H, GCFGLH: F0323H

b15 b14 b13 b12 b11 b10 b9 b8 b7 b6 b5 b4 b3 b2 b1 b0

— — — TSSS TSP[3:0] — — — DCS MME DRE DCE TPRI

After Reset 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0

Bit Symbol Bit Name Description R/W

15 to

13

— Reserved These bits are always read as 0. The write value should

always be 0.

R

12 TSSS Timestamp Clock Source Select 0: Clock obtained by frequency-dividing fCLK by 2 (fCLK/2)

1: CANi bit time clock

R/W

11 to 8 TSP[3:0] Timestamp Clock Source Division

b11 b10 b9 b8

0 0 0 0 : Not divided

0 0 0 1 : Divided by 2

0 0 1 0 : Divided by 4

0 0 1 1 : Divided by 8

0 1 0 0 : Divided by 16

0 1 0 1 : Divided by 32

0 1 1 0 : Divided by 64

0 1 1 1 : Divided by 128

1 0 0 0 : Divided by 256

1 0 0 1 : Divided by 512

1 0 1 0 : Divided by 1024

1 0 1 1 : Divided by 2048

1 1 0 0 : Divided by 4096

1 1 0 1 : Divided by 8192

1 1 1 0 : Divided by 16384

1 1 1 1 : Divided by 32768

R/W

7 to 5 — Reserved These bits are always read as 0. The write value should

always be 0.

R

4 DCS CAN Clock Source Select 0: Clock obtained by frequency-dividing fCLK by 2 (fCLK/2)

1: X1 clock (fx)

R/W

3 MME Mirror Function Enable 0: Mirror function is disabled.

1: Mirror function is enabled.

R/W

2 DRE DLC Replacement Enable 0: DLC replacement is disabled.

1: DLC replacement is enabled.

R/W

1 DCE DLC Check Enable 0: DLC check is disabled.

1: DLC check is enabled.

R/W

0 TPRI Transmit Priority Select 0: ID priority

1: Transmit buffer number priority

R/W

Modify the GCFGL register only in global reset mode.

• TSSS Bit

This bit is used to select a clock source of the timestamp counter.

• TSP[3:0] Bits

The clock obtained by dividing the clock source (selected by the TSSS bit) by the TSP[3:0] value is the count

source of the timestamp counter.

Loading...

Loading...