RL78/F13, F14 CHAPTER 7 TIMER RJ

R01UH0368EJ0210 Rev.2.10 548

Dec 10, 2015

7.3.4 Timer RJ Counter Register 0 (TRJ0), Timer RJ Reload Register

TRJ0 is a 16-bit register. The write value is written to the reload register and the read value is read from the counter.

The states of the reload register and the counter are changed depending on the TSTART bit in the TRJCR0 register.

For details, see 7. 4. 1 Reload Register and Counter Rewrite Operation.

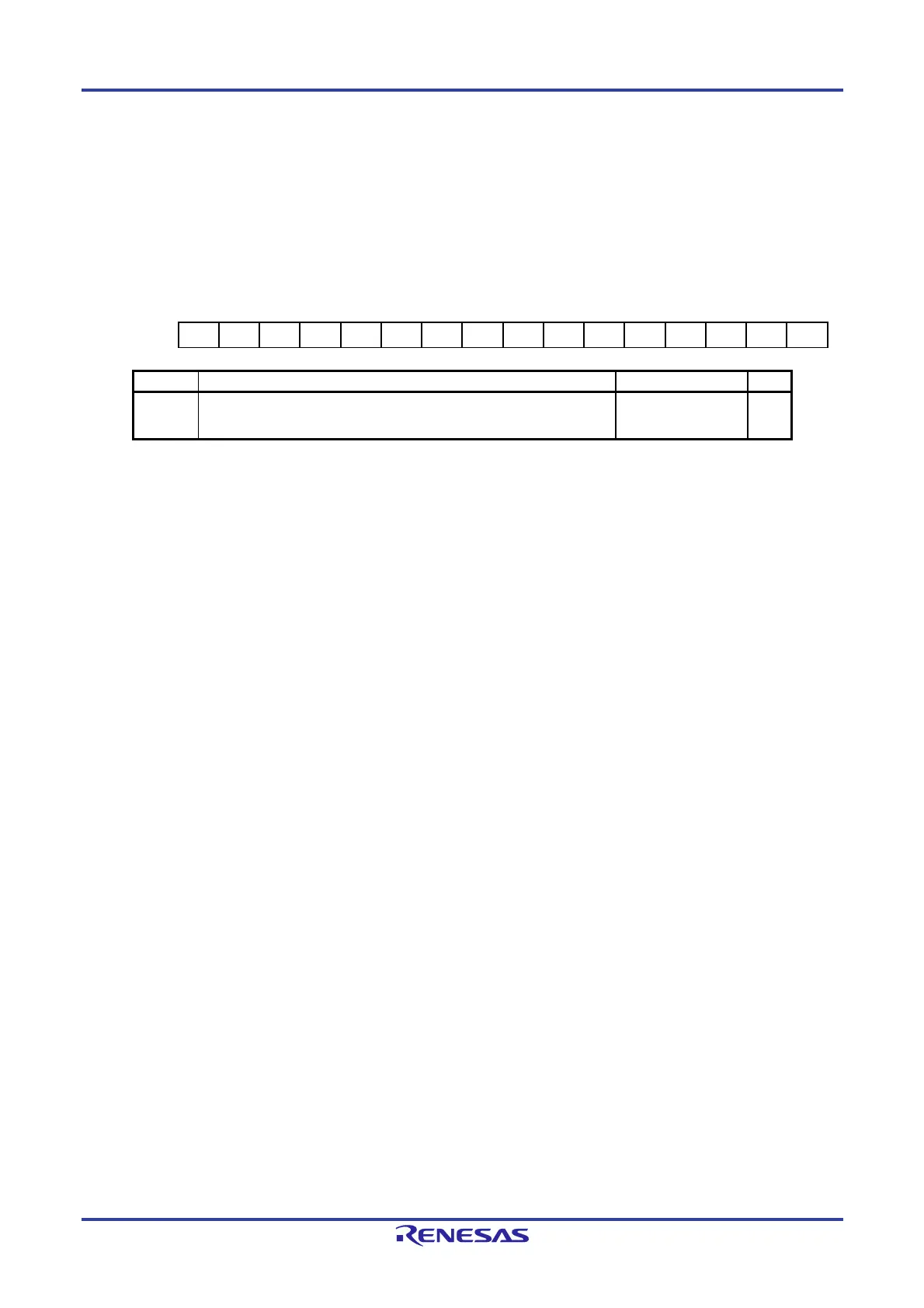

Figure 7-5. Format of Timer RJ Counter Register 0 (TRJ0), Timer RJ Reload Register

Address : F06F0H After Reset: FFFFH

Symbol 15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

TRJ0

— Function Setting Range R/W

Bits

15 to 0

16-bit counter and reload register

Notes 1, 2, 3

0000H to FFFFH R/W

Notes 1. When 1 is written to the TSTOP bit in the TRJCR0 register, the 16-bit counter is forcibly stopped and set to

FFFFH.

2. The TRJ0 register must be accessed in 16-bit units. Do not access this register in 8-bit units.

3. When the setting of bits TCK2 to TCK0 in the TRJMR0 register is other than 001B (fCLK/8) or 011B (fCLK/2),

if the TRJ0 register is set to 0000H, a request signal to the data transfer controller (DTC) and the event link

controller (ELC) is generated only once immediately after the count starts. However, the TRJO0 and TRJIO0

output is toggled.

When the TRJ0 register is set to 0000H in event counter mode, regardless of the value of bits TCK2 to TCK0,

a request signal to the DTC, ELC, and interrupt functions is generated only once immediately after the count

starts. In addition, the TRJO0 output is toggled even during a period other than the specified count period.

When the TRJ0 register is set to 0000H or a higher value, a request signal is generated each time TRJ

underflows.

Caution When the TRJ0 register is accessed, the CPU does not proceed to the next instruction

processing but enters the wait state for CPU processing. For this reason, if this wait state

occurs, the number of instruction execution clocks is increased by the number of wait clocks.

The number of wait clocks for access to the TRJ0 register is one clock for both writing and

reading.

Loading...

Loading...