RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1305

Dec 10, 2015

18.3.14 CAN Global Error Flag Register (GERFLL)

Address GERFLL: F032CH

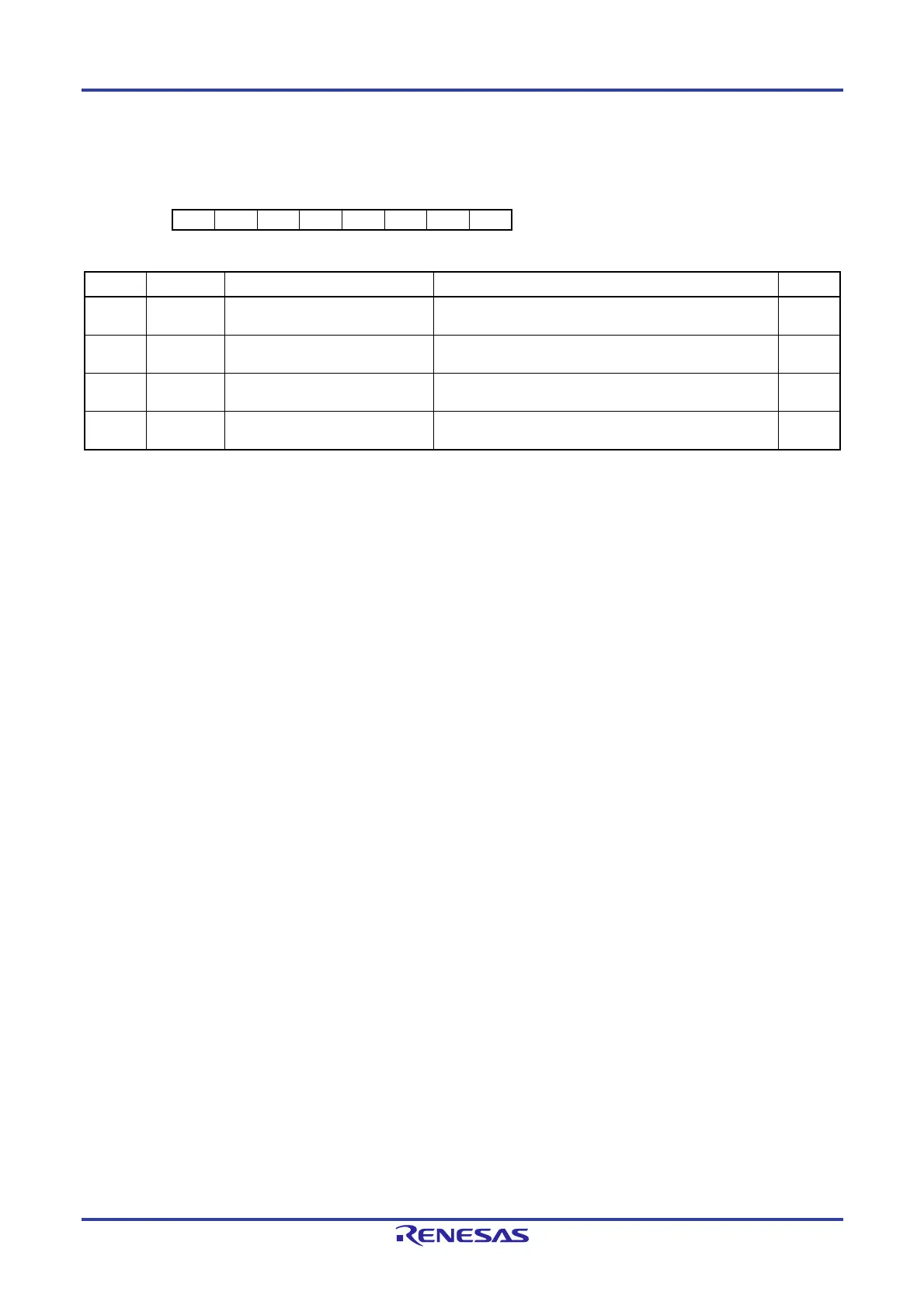

b7 b6 b5 b4 b3 b2 b1 b0

— — — — — THLES MES DEF

After Reset 0 0 0 0 0 0 0 0

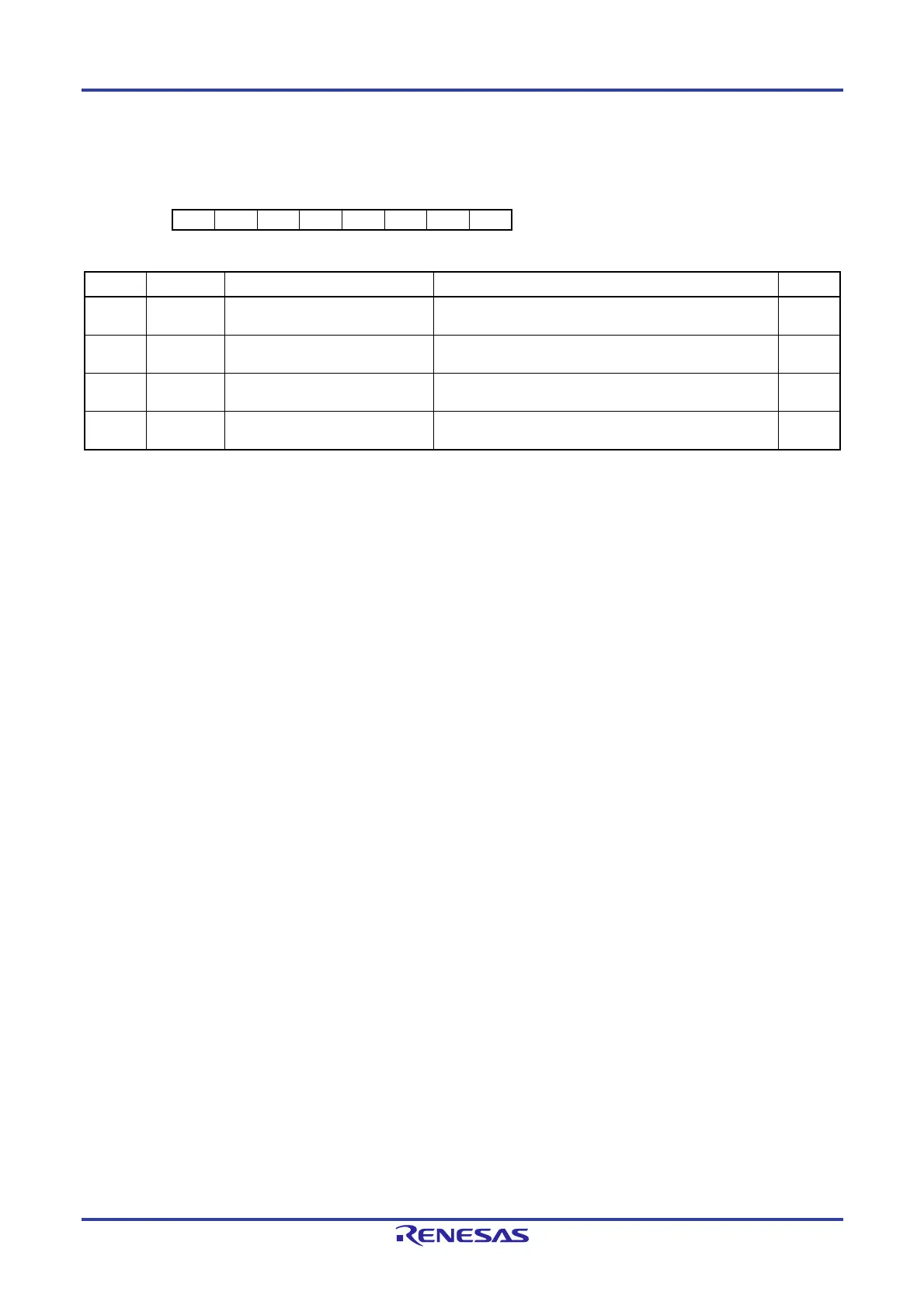

Bit Symbol Bit Name Description R/W

7 to 3 — Reserved The read value is undefined. The write value should always

be 0.

R

2 THLES Transmit History Buffer Overflow

Status Flag

0: No transmit history buffer overflow is present.

1: A transmit history buffer overflow is present.

R

1 MES FIFO Message Lost Status Flag 0: No FIFO message lost error is present.

1: A FIFO message lost error is present.

R

0 DEF DLC Error Flag 0: No DLC error is present.

1: A DLC error is present.

R/(W)

Note

Note The only effective value for writing to this flag bit is 0, which clears the bit. Otherwise writing to the bit results in

retention of its state. To write 0 to this flag bit, write by using an 8-bit data transfer instruction.

All flags in the GERFLL register are cleared to 0 in global reset mode.

• THLES Flag

The THLES flag is set to 1 when the THLELT flag in the THLSTSi register is set to 1.

This flag is cleared to 0 when the THLELT flag is set to 0.

• MES Flag

The MES flag is set to 1 when any one of the RFMLT flags in the RFSTSm register (m = 0, 1) or the CFMLT flag

in the CFSTSk register is set to 1.

This flag is cleared to 0 when all RFMLT flags and the CFMLT flag are set to 0.

• DEF Flag

The DEF flag is set to 1 when an error has been detected during the DLC check. This flag can be cleared to 0

by writing 0 by the program.

<R>

Loading...

Loading...