RL78/F13, F14 CHAPTER 18 CAN INTERFACE (RS-CAN LITE)

R01UH0368EJ0210 Rev.2.10 1403

Dec 10, 2015

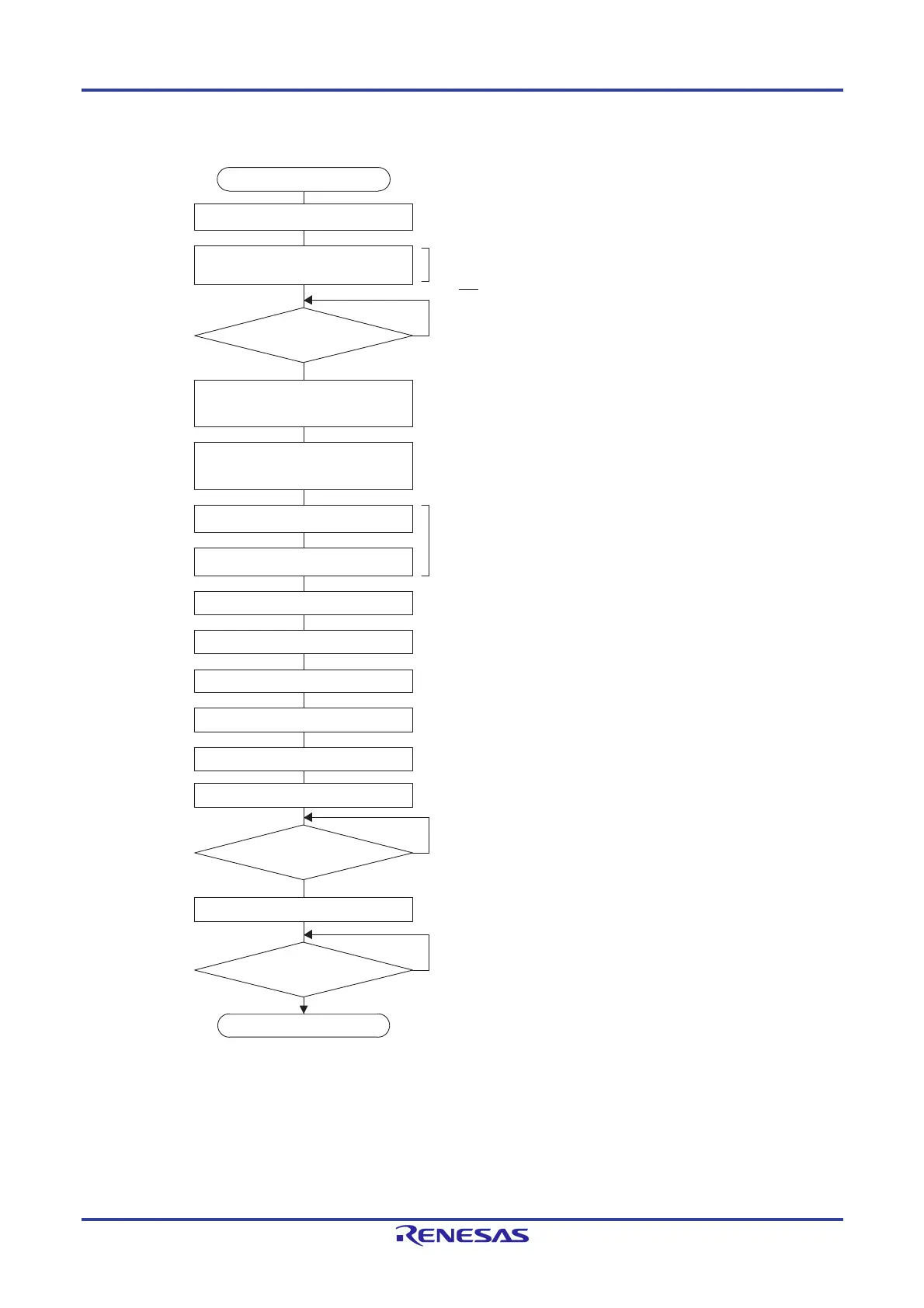

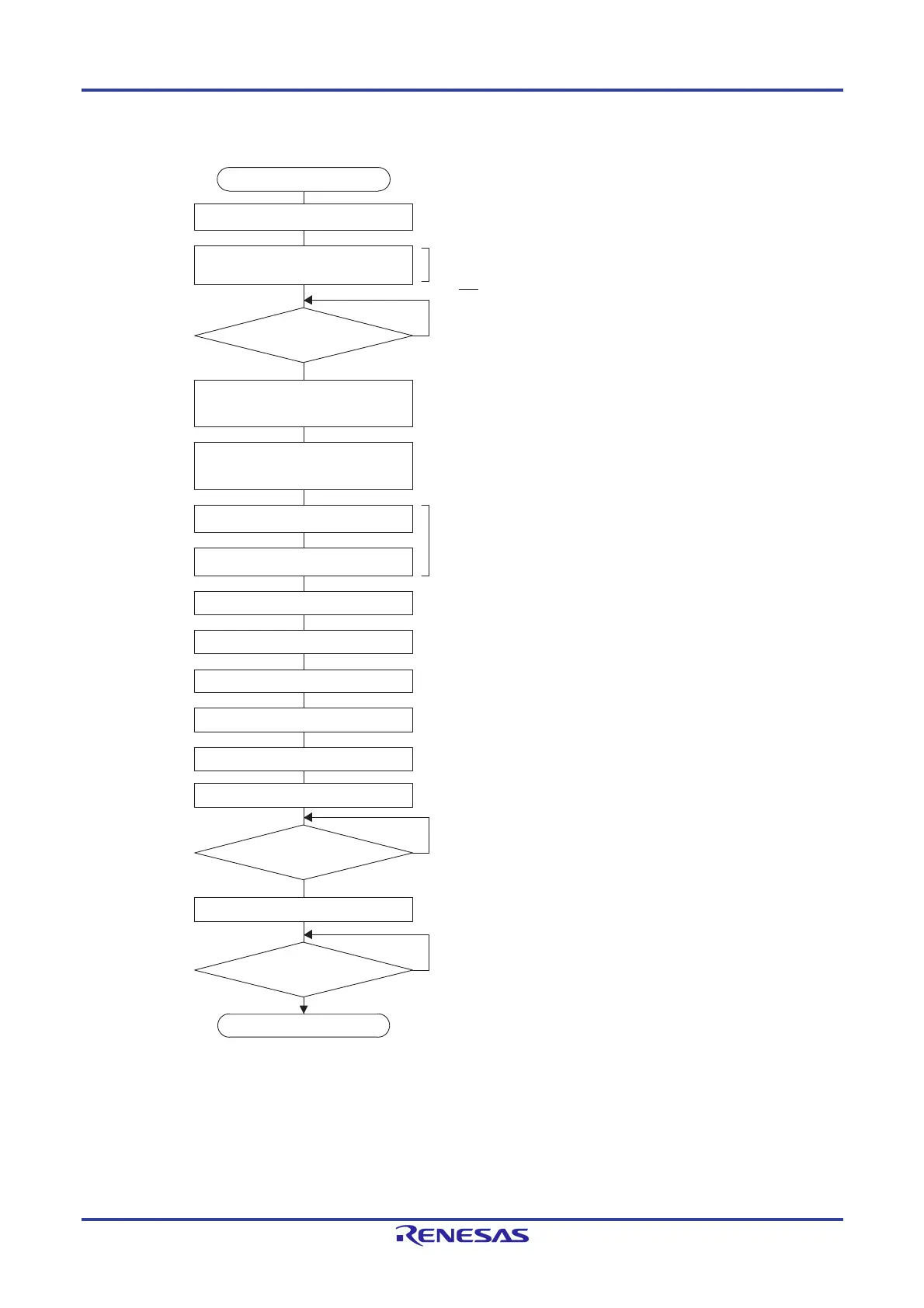

Figure 18-16. CAN Setting Procedure after the Operation of the CAN Module is Enabled

Start

End

Receive rule setting

Interrupt setting

Transition to global operating mode

Buffer setting

Global interrupt

Channel interrupt, bus off recovery, error indication

Interrupt control registers of interrupt controller

·

This setting is not required when fx is not in use.

·

When fx is to be selected,

the following condition must be satisfied.

·

Clock

·

Bit timing

·

Communication speed

·

Timestamp

·

Mirror function

·

DLC filter

·

Transmit priority

GAFLCFG register

GAFLIDLj, GAFLIDHj, GAFLMLj, GAFLMHj, GAFLPLj, and GAFLPHj registers

Receive buffer, receive FIFO buffer, transmit/receive FIFO buffer,

transmit buffer, transmit history buffer

Enable the CAN module.

(Set the CAN0EN bit in the PER2 register to 1)

Start supply of the CAN clock.

(Set the CAN0MCKE bit in the CANCKSEL register

to 1)

Is the GRAMINIT flag in the

GSTS register 0?

Transition from global stop mode

to global reset mode

(Set the GSLPR bit in the GCTRL register to 0)

Transition from channel stop mode

to channel reset mode

(Set the CSLPR bit in the CiCTRL register to 0)

Setting of GCFGH and GCFGL registers

Setting of CiCFGH and CiCFGL registers

GCTRL register setting

CiCTRL register setting

Remark i = 0

j = 0 to 15

Notes 1. If the high-speed system clock (f

MX

) is to be selected as the LIN communications clock source, and the highspeed

on-chip oscillator clock (f

IH

) or the PLL clock with its source as the high-speed on-chip oscillator clock is to

be selected as the source of the clock signal for f

CLK

, make sure that the condition (LIN communications clock

source) < f

CLK

is satisfied.

2. If the high-speed system clock is to be selected as f

CLK

, do not select f

X

as f

CAN

.

No

Yes

Has the transition to global operating

mode been completed?

No

Yes

f

X

≤

2

f

CLK

Note 1

Transition to channel communication mode

Has the transition to

channel communication mode been

completed?

No

Yes

Note 2

Notes 2, 3

Loading...

Loading...