RL78/F13, F14 CHAPTER 19 DTC

R01UH0368EJ0210 Rev.2.10 1427

Dec 10, 2015

Notes 1. In the HALT, STOP, and SNOOZE modes, these areas cannot be set as the sources for DTC transfer since

the flash memory is stopped.

2. High-speed transfer is enabled only for the 1st SFR area and the 2nd SFR area.

Remark Products of groups A, B, C, and D: i = 0 to 4, j = 0 to 23, m = 0, 1

Products of group E: i = 0 to 5, j = 0 to 23, m = 0, 1

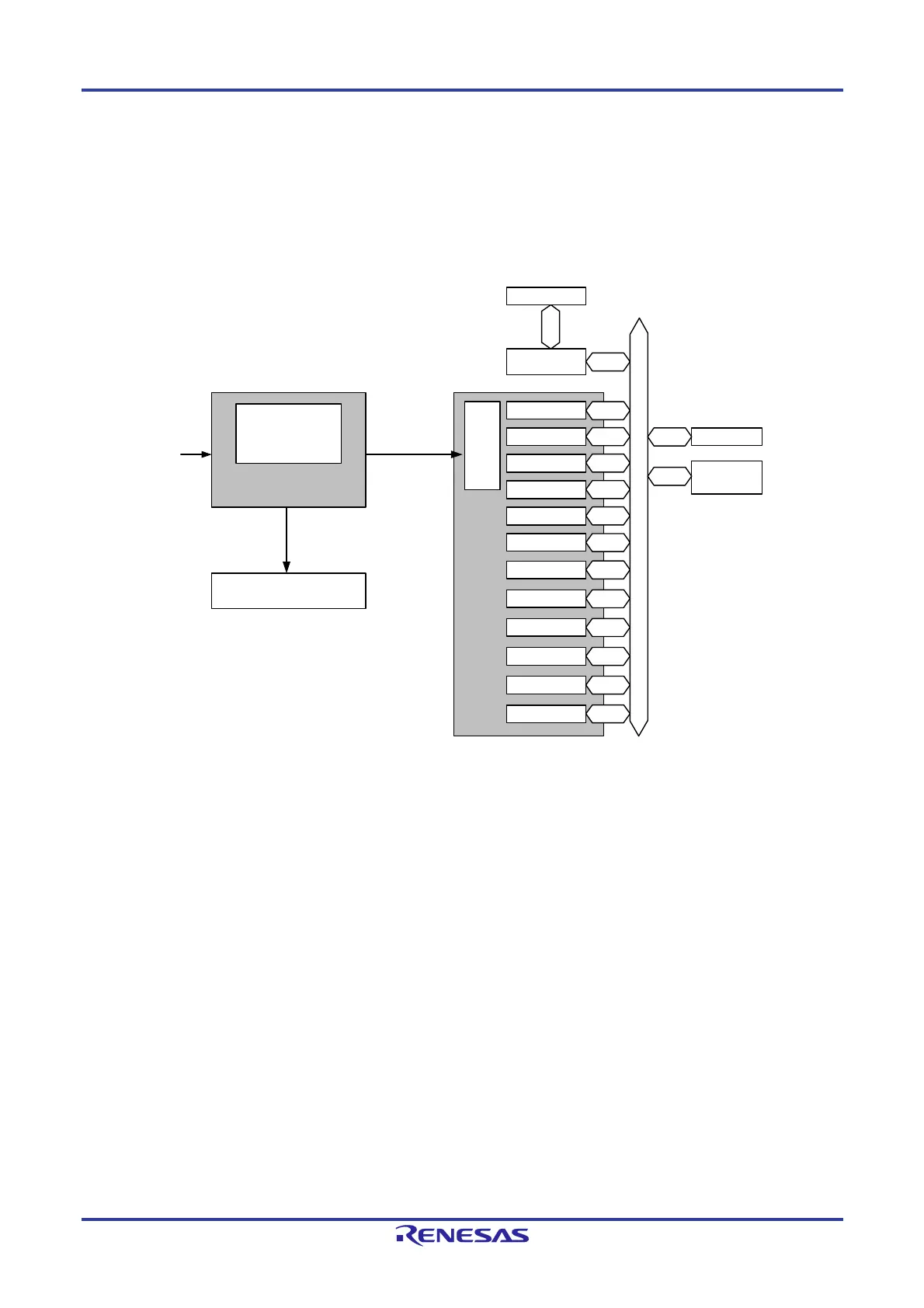

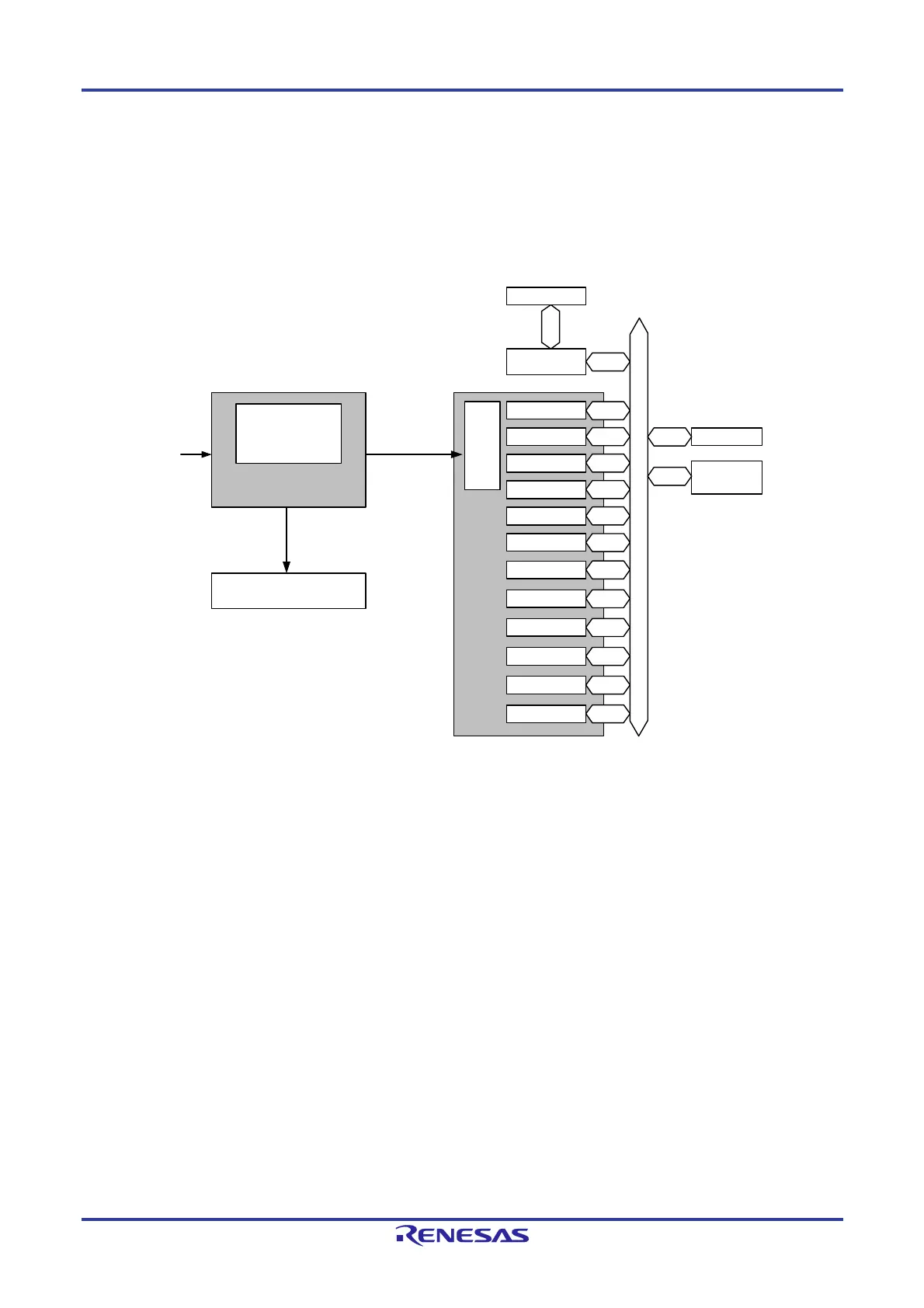

Figure 19-1. DTC Block Diagram

DTCEN0

to

DTCEN5

Note

Interrupt controller

DTCCRj

DTBLSj

DTCCTj

DTRLDj

DTSARj

DTDARj

DTC

activation

request

Peripheral interrupt

request

CPU

Peripheral

functions

Note Products of groups A, B, C, and D do not have the DTCEN5 register.

Remark j = 0 to 23, m = 0, 1

DTCCRj: DTC control register j

DTBLSj: DTC block size register j

DTCCTj: DTC transfer count register j

DTRLDj: DTC transfer count reload register j

DTSARj: DTC source address register j

DTDARj: DTC destination address register j

DTCEN0 to DTCEN5

Note

: DTC activation enable registers 0 to 5

Note

SELHSm: High-speed DTC channel select register m

HDTCCRm: High-speed DTC control register m

HDTCCTm: High-speed DTC transfer count register m

HDTRLDm: High-speed DTC transfer count reload register m

HDTSARm: High-speed DTC source address register m

HDTDARm: High-speed DTC destination address register m

Control circuit

Internal bus

e

ip

e

al in

e

up

eques

ROM

RAM

SELHSm

HDTCCRm

HDTCCTm

HDTRLDm

HDTSARm

HDTDARm

Loading...

Loading...