RL78/F13, F14 CHAPTER 21 INTERRUPT FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1498

Dec 10, 2015

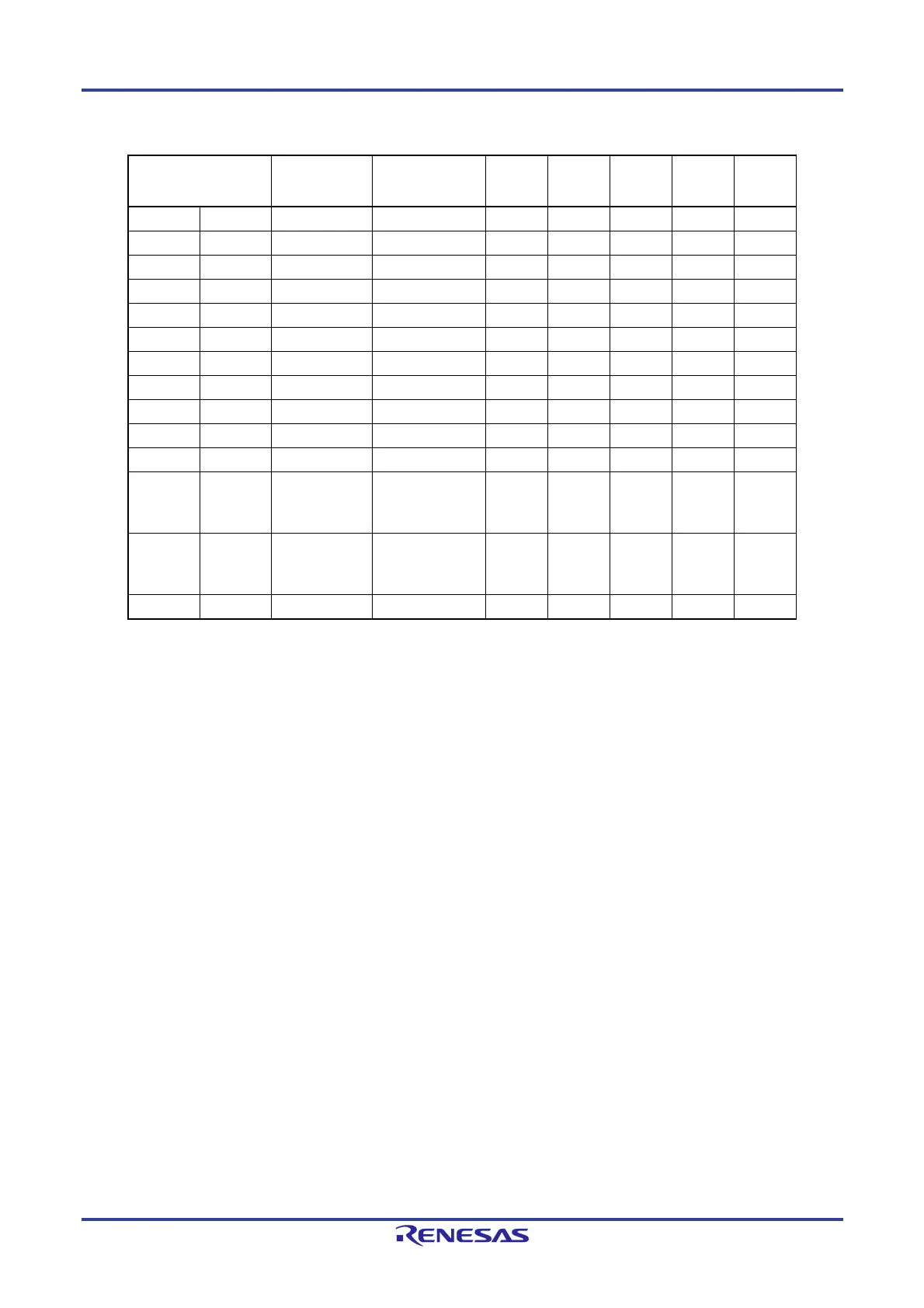

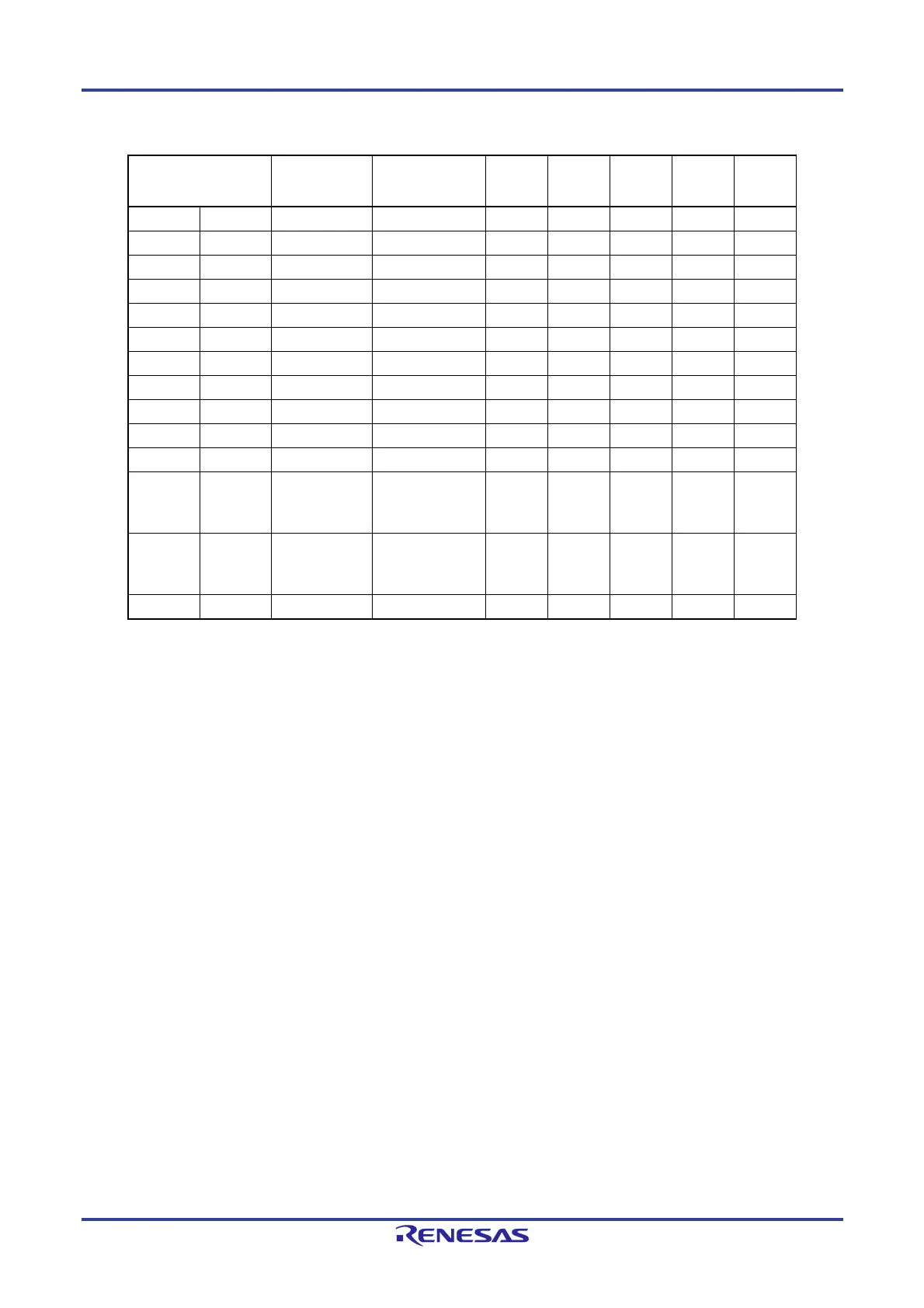

Table 21-3. Ports Corresponding to EGPn and EGNn bits

Detection Enable Bit

Edge Detection

Port

Interrupt

Request Signal

80, 100-

pin

64-pin 48-pin

30, 32-

pin

20-pin

EGP0 EGN0 P137 INTP0

EGP1 EGN1 P125 INTP1

EGP2 EGN2 P30(P31) INTP2

EGP3 EGN3 P17 (P50) INTP3

EGP4 EGN4 P120 INTP4

EGP5 EGN5 P12 INTP5

EGP6 EGN6 P71 INTP6

EGP7 EGN7 P32 INTP7

EGP8 EGN8 P70 INTP8

Note 1

Note 1

EGP9 EGN9 P00 INTP9

Note 1

Note 1

EGP10 EGN10 P53 INTP10

Note 1

EGP11 EGN11 P51

INTP11/

INTLIN0WUP

Note

2

EGP12 EGN12 P77

INTP12/

INTLIN1WUP

Note

2

Note 3

Note 3

EGP13 EGN13 P47 INTP13

Note 3

Notes 1. Not provided in Group A products.

2. Set the EGP1 and EGN1 registers before the INTLIN0WUP and INTLIN1WUP interrupts are

generated.

3. Provided only in Group E products.

Caution When the input port pins used for the external interrupt functions are switched to the output

mode, the INTPn interrupt might be generated upon detection of a valid edge. When

switching the input port pins to the output mode, set the port mode register (PMxx) to 0 after

disabling the edge detection (by setting EGPn and EGNn to 0).

Remarks 1. For edge detection ports, see 2.1 Pin Function List.

2. n = 0 to 13

Loading...

Loading...