RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 142

Dec 10, 2015

R5F10PmF (m = G, L, M): FE500H to FE52FH

R5F10PmJ (m = G, L, M, P): FB500H to FB52FH

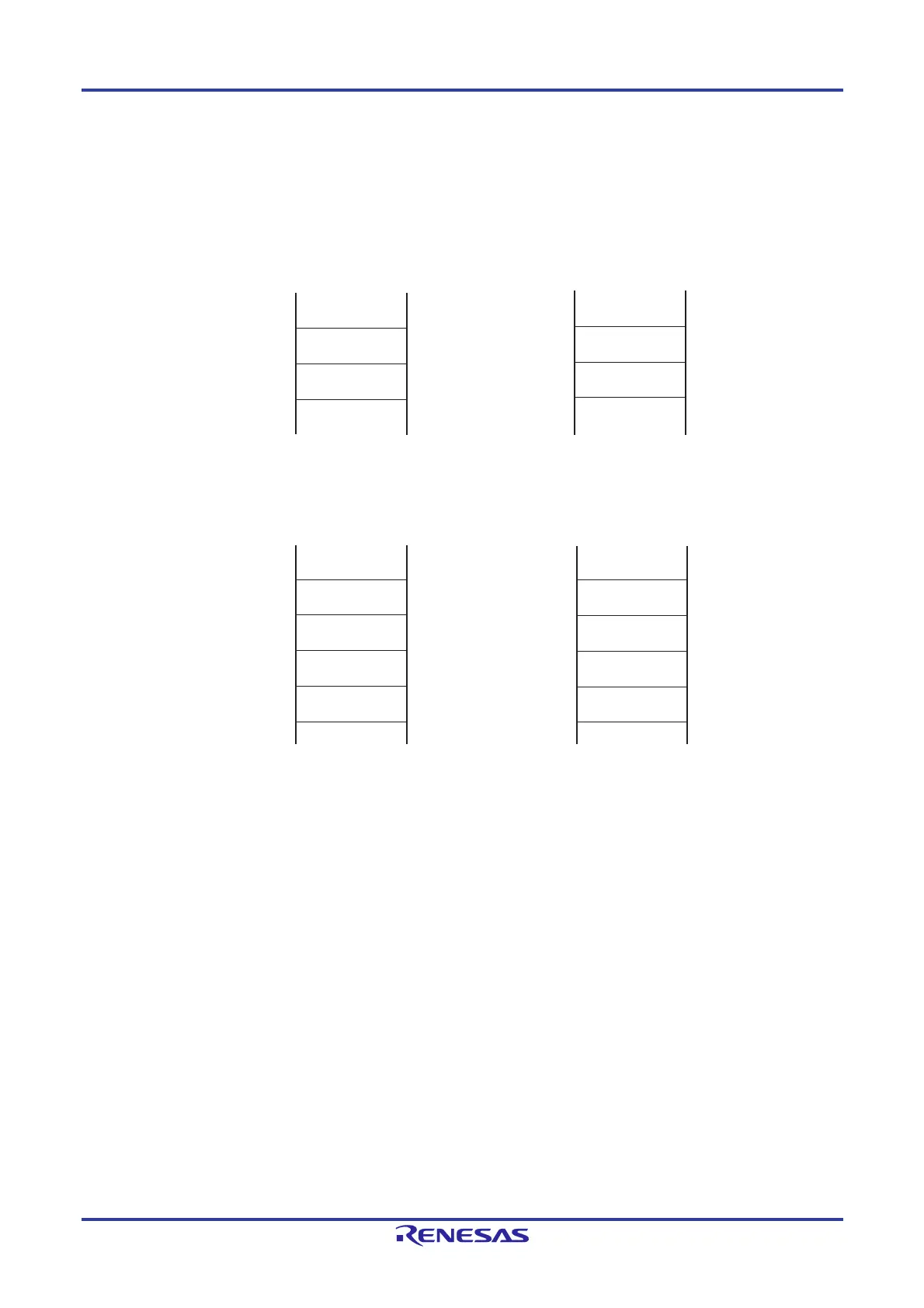

Figure 3-39. Data to Be Saved to Stack Memory

PC7 to PC0

PC15 to PC8

PC19 to PC16

PSW

Interrupt, BRK instruction

SP←SP−4

↑

SP−4

↑

SP−3

↑

SP−2

↑

SP−1

↑

SP →

CALL, CALLT instructions

Register pair lower

Register pair higher

PUSH rp instruction

SP←SP−2

↑

SP−2

↑

SP−1

↑

SP →

(4-byte stack)

(4-byte stack)

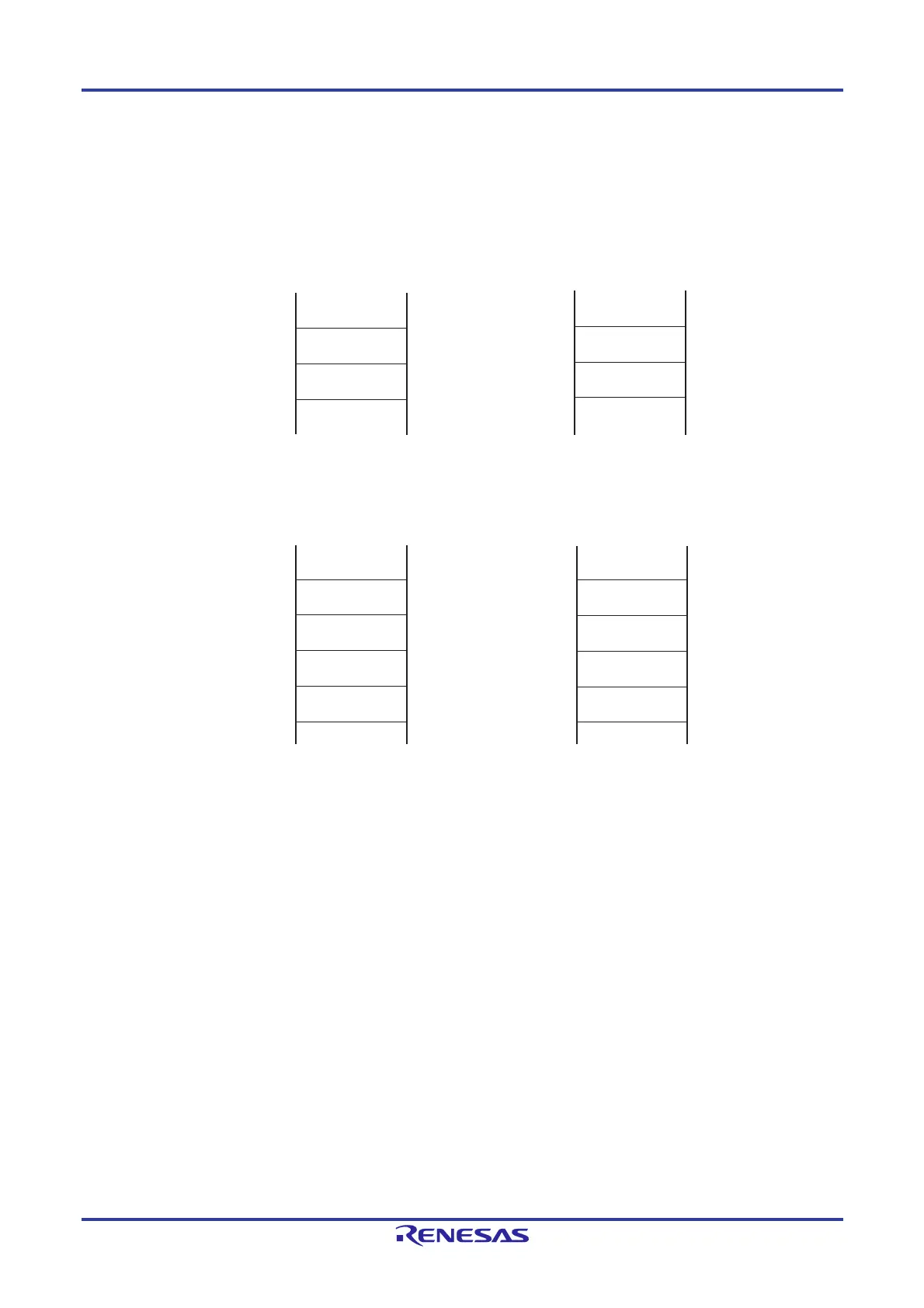

PC7 to PC0

PC15 to PC8

PC19 to PC16

00H

SP←SP−4

↑

SP−4

↑

SP−3

↑

SP−2

↑

SP−1

↑

SP →

00H

PSW

PUSH PSW instruction

SP←SP−2

↑

SP−2

↑

SP−1

↑

SP →

Loading...

Loading...