General-Purpose Digital I/O

C2000 Microcontroller Workshop - System Initialization 5 - 13

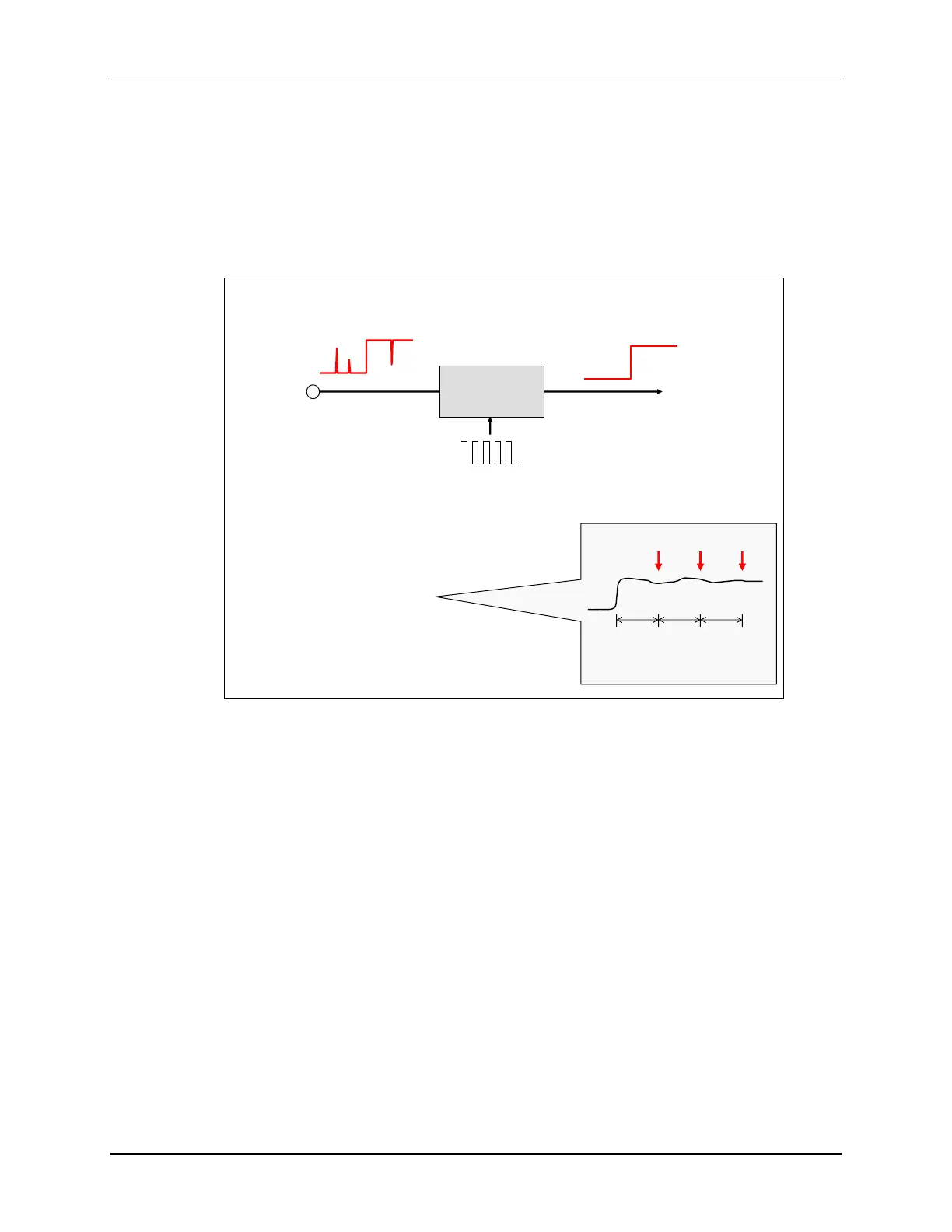

The GPIO pin block diagram shows a single GPIO pin. If the pin is set as a GPIO by the GPIO

multiplexer, the direction will be set by the GPIO direction register. The GPIO data register will

have the value of the pin if set as an input or write the value of the data register to the pin if set as

an output.

The data register can be quickly and easily modified using set, clear, or toggle registers. As you

can see, the GPIO multiplexer can be set to select up to three other possible peripheral pin

assignments. Also, the pin has an option for an internal pull-up.

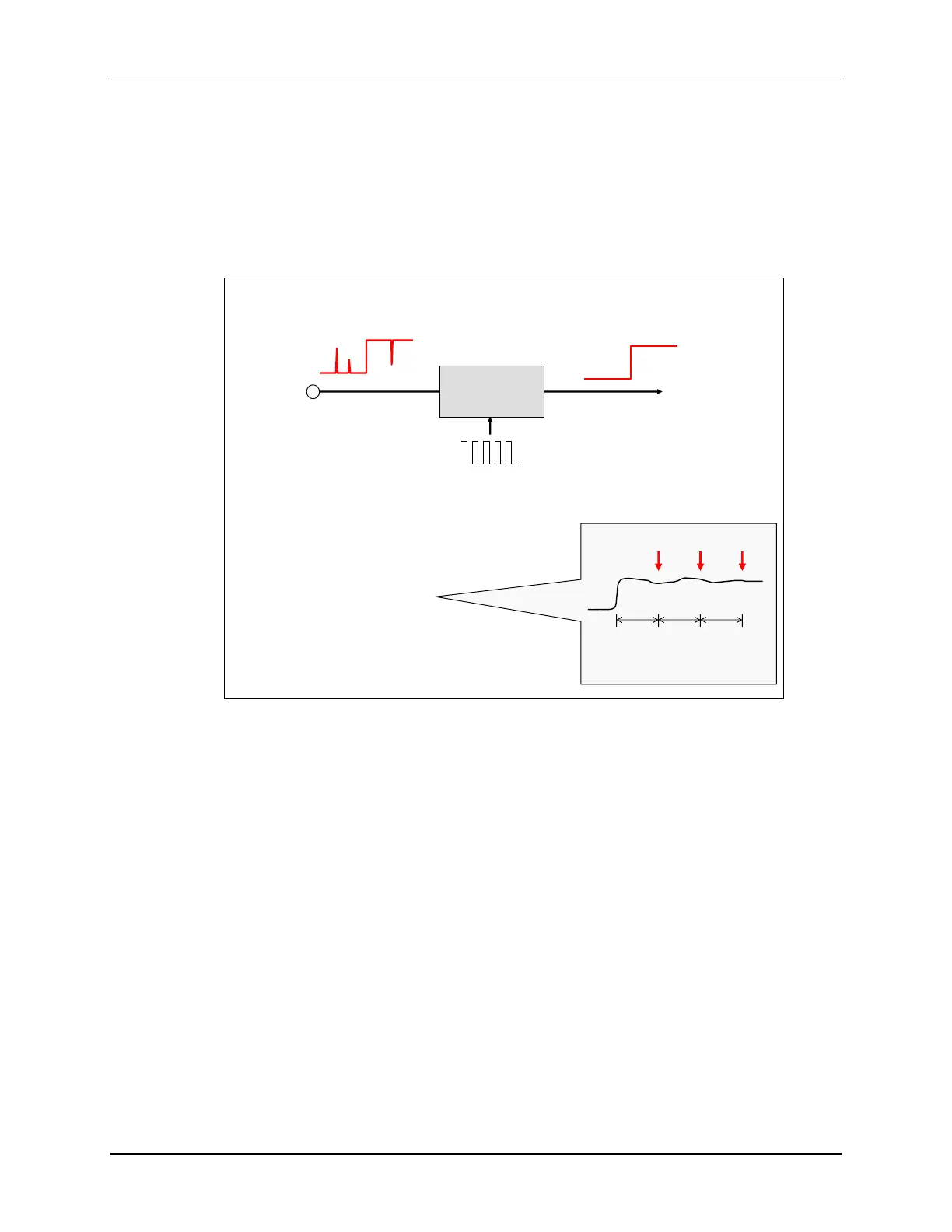

F2806x GPIO Input Qualification

Qualification available on ports A & B only

Individually selectable per pin

no qualification (peripherals only)

sync to SYSCLKOUT only

qualify 3 samples

qualify 6 samples

AIO pins are fixed as

‘sync to SYSCLKOUT’

Input

Qualification

pin

to GPIO and

peripheral

modules

SYSCLKOUT

T

T T

samples taken

T = qual period

The GPIO input qualification feature allows filtering out noise on a pin. The user would select

the number of samples and qualification period. Qualification is available on ports A and B only

and is individually selectable per pin.

Loading...

Loading...