F2806x GPIO Input Qual Registers

GpioCtrlRegs.register (lab file: Gpio.c)

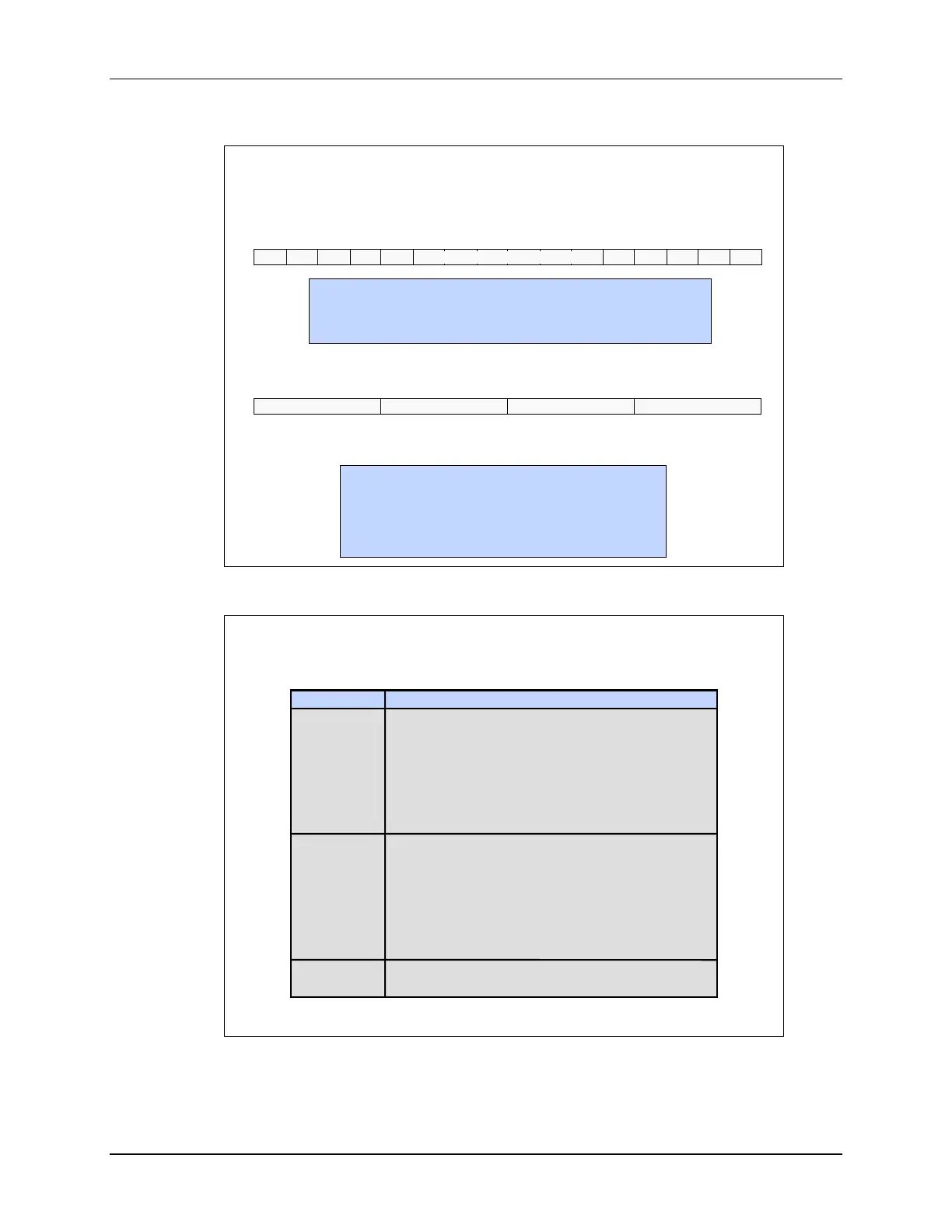

00 = sync to SYSCLKOUT only *

01 = qual to 3 samples

10 = qual to 6 samples

11 = no sync or qual (for peripheral only; GPIO same as 00)

00h no qualification (SYNC to SYSCLKOUT) *

01h QUALPRD = SYSCLKOUT/2

02h QUALPRD = SYSCLKOUT/4

… … …

FFh QUALPRD = SYSCLKOUT/510

GPAQSEL1 / GPAQSEL2 / GPBQSEL1

16 pins configured per register

0

31

QUALPRD0QUALPRD1QUALPRD2QUALPRD3

GPACTRL / GPBCTRL

31 24 16 8 0

B: GPIO56-63 GPIO48-55 GPIO47-40 GPIO39-32

A: GPIO31-24 GPIO23-16 GPIO15-8 GPIO7-0

* reset default

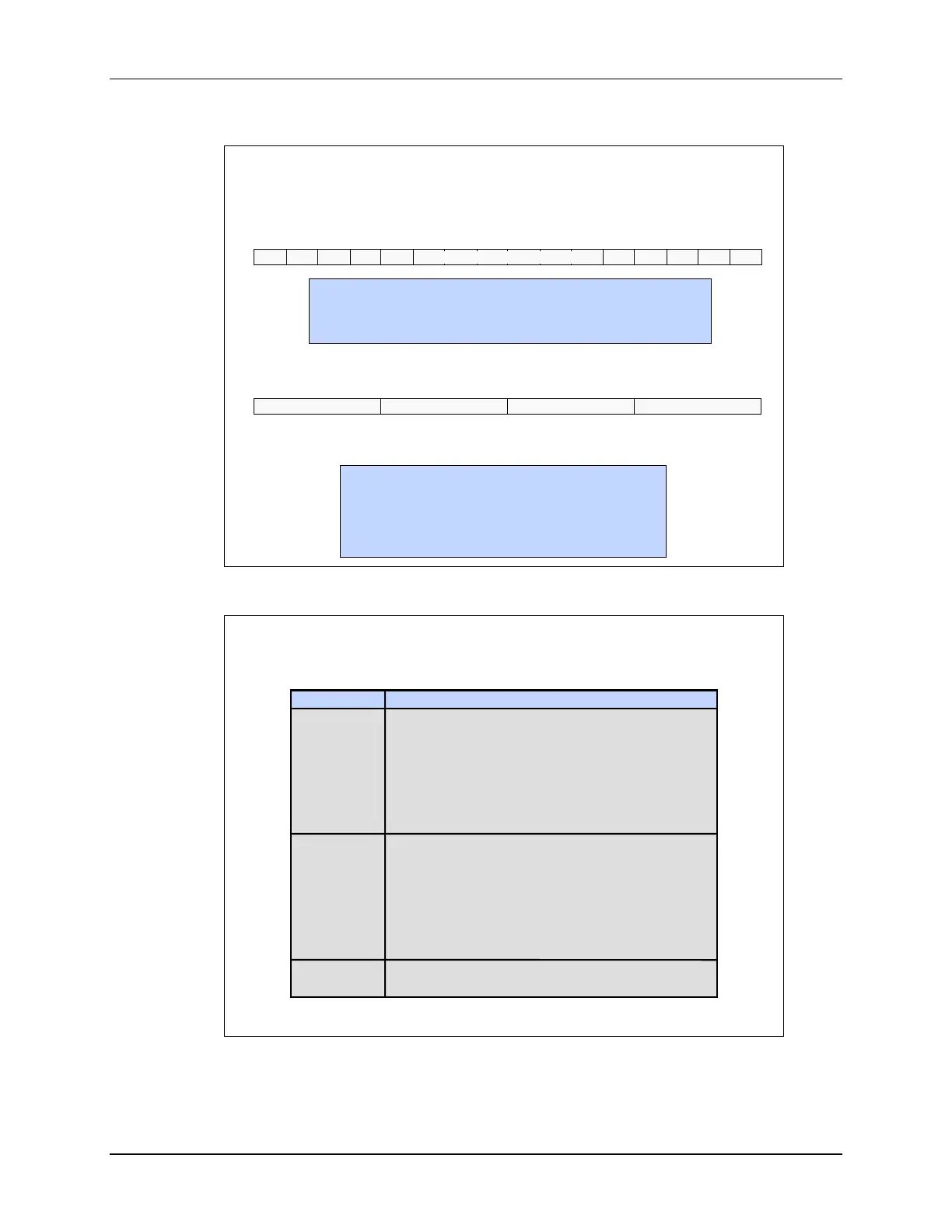

F2806x GPIO Control Registers

GpioCtrlRegs.register (lab file: Gpio.c)

Register Description

GPACTRL GPIO A Control Register [GPIO 0 – 31]

GPAQSEL1 GPIO A Qualifier Select 1 Register [GPIO 0 – 15]

GPAQSEL2 GPIO A Qualifier Select 2 Register [GPIO 16 – 31]

GPAMUX1 GPIO A Mux1 Register [GPIO 0 – 15]

GPAMUX2 GPIO A Mux2 Register [GPIO 16 – 31]

GPADIR GPIO A Direction Register [GPIO 0 – 31]

GPAPUD GPIO A Pull-Up Disable Register [GPIO 0 – 31]

GPBCTRL GPIO B Control Register [GPIO 32 – 63]

GPBQSEL1 GPIO B Qualifier Select 1 Register [GPIO 32 – 47]

GPBQSEL2 GPIO B Qualifier Select 2 Register [GPIO 48 – 63]

GPBMUX1 GPIO B Mux1 Register [GPIO 32 – 47]

GPBMUX2 GPIO B Mux2 Register [GPIO 48 – 63]

GPBDIR GPIO B Direction Register [GPIO 32 – 63]

GPBPUD GPIO B Pull-Up Disable Register [GPIO 32 – 63]

AIOMUX1 ANALOG I/O Mux1 Register [AIO 0 – 15]

AIODIR ANALOG I/O Direction Register [AIO 0 – 15]

Loading...

Loading...