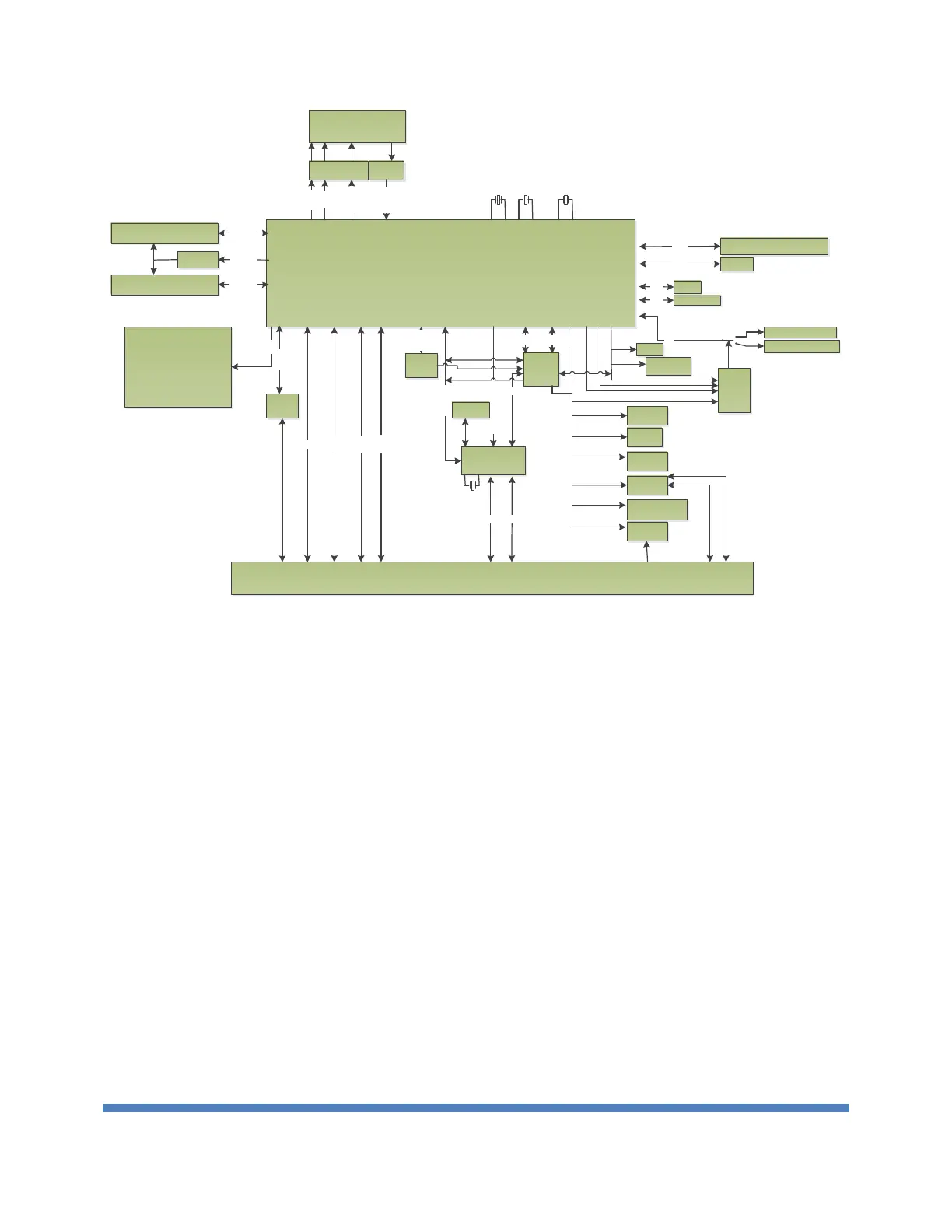

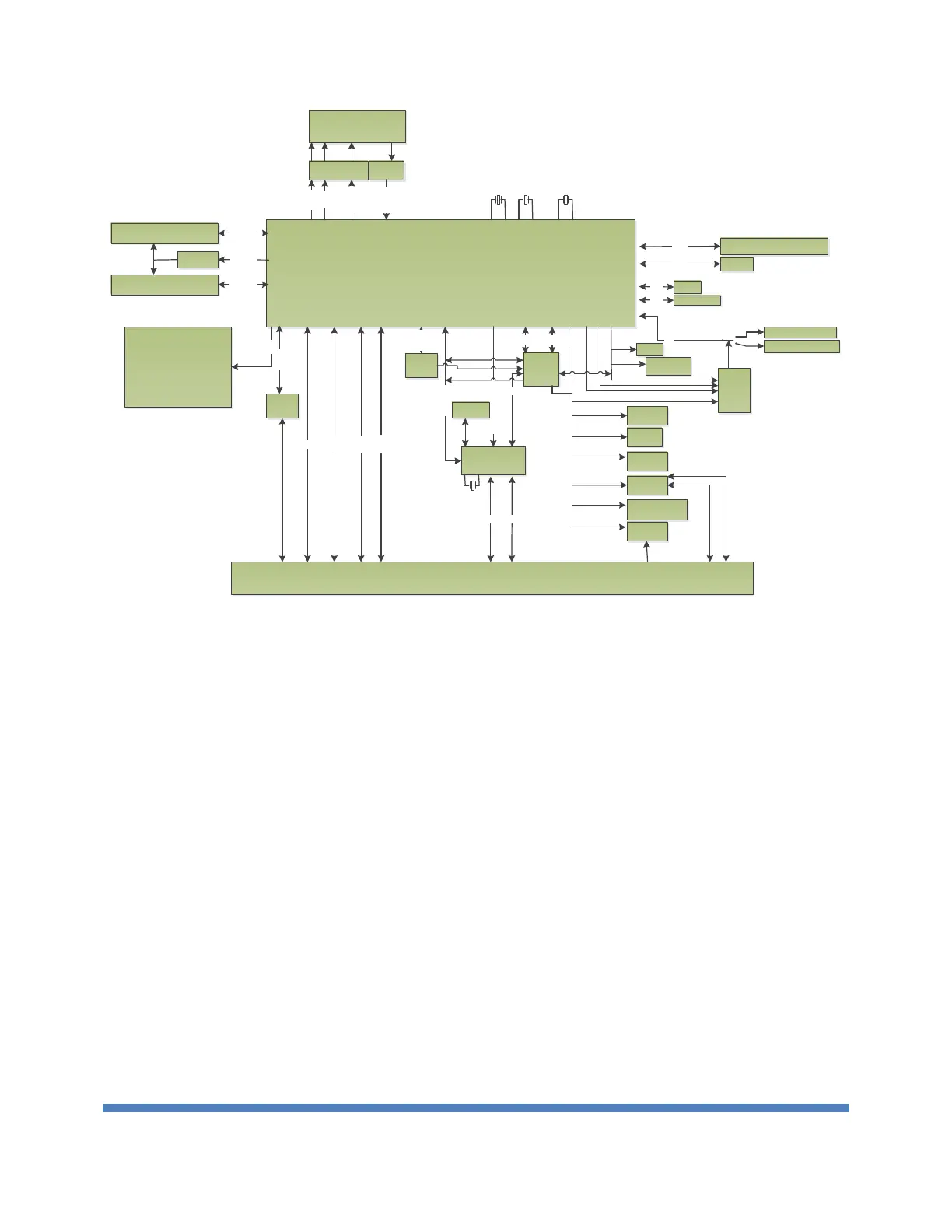

2.2.1. Clock Tree

The unit support has a Synchronous logic which consists of Network Interface Synchronizer

chip, Jitter attenuators and clock buffers. The key component is a Network Interface Synchronizer

chip.

The Network Interface Synchronizer chip selects a reference clock from one of two valid clock

sources generating a Stratum 3 compliant reference clock for the Broadcom Trident chip. This clock

is also used as a transmit reference clock for all external interface ports. This logic consists of a IDT

89307 Network Interface Synchronizer chip and Oven controlled crystal oscillator. This synchronizer

chip when properly configured will produce 25MHz and 156.25MHz clock which is frequency locked

to a selected port recovered clock.

The IDT 89307 is configured through an I2C interface, it reports major state information via a

number of status and control signals.

Figure 3 Switch board clock Tree

Loading...

Loading...