ONIE: / # update_url tftp://”TFTP_server_IP”/”file_name.updater”

5.12.9.3. Operational mode

The real-time ISP feature present in the Max V family is used for upgrade CPLD code.

5.12.9.4. Time Required to Download New CPLD Image

It will take 20 sec for updating Main board CPLD code and 10 sec for updating Fan board

CPLD code.

5.12.9.5. Power cycling requirements

The system needs a power cycle after finish CPLD code update. It will run original CPLD

code before power cycle.

5.13. IDT 8V89307

5.13.1. Configurations of IDT 8V89307

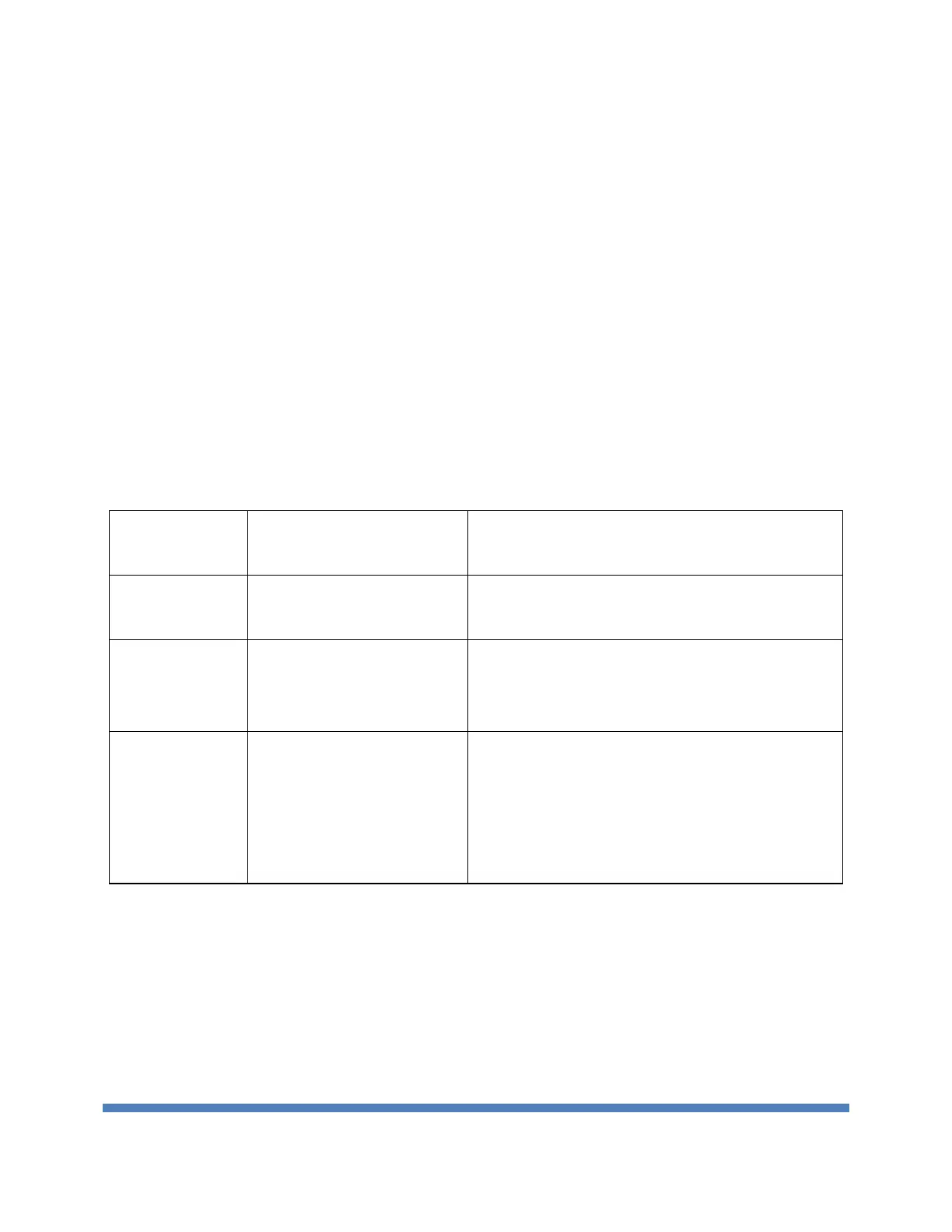

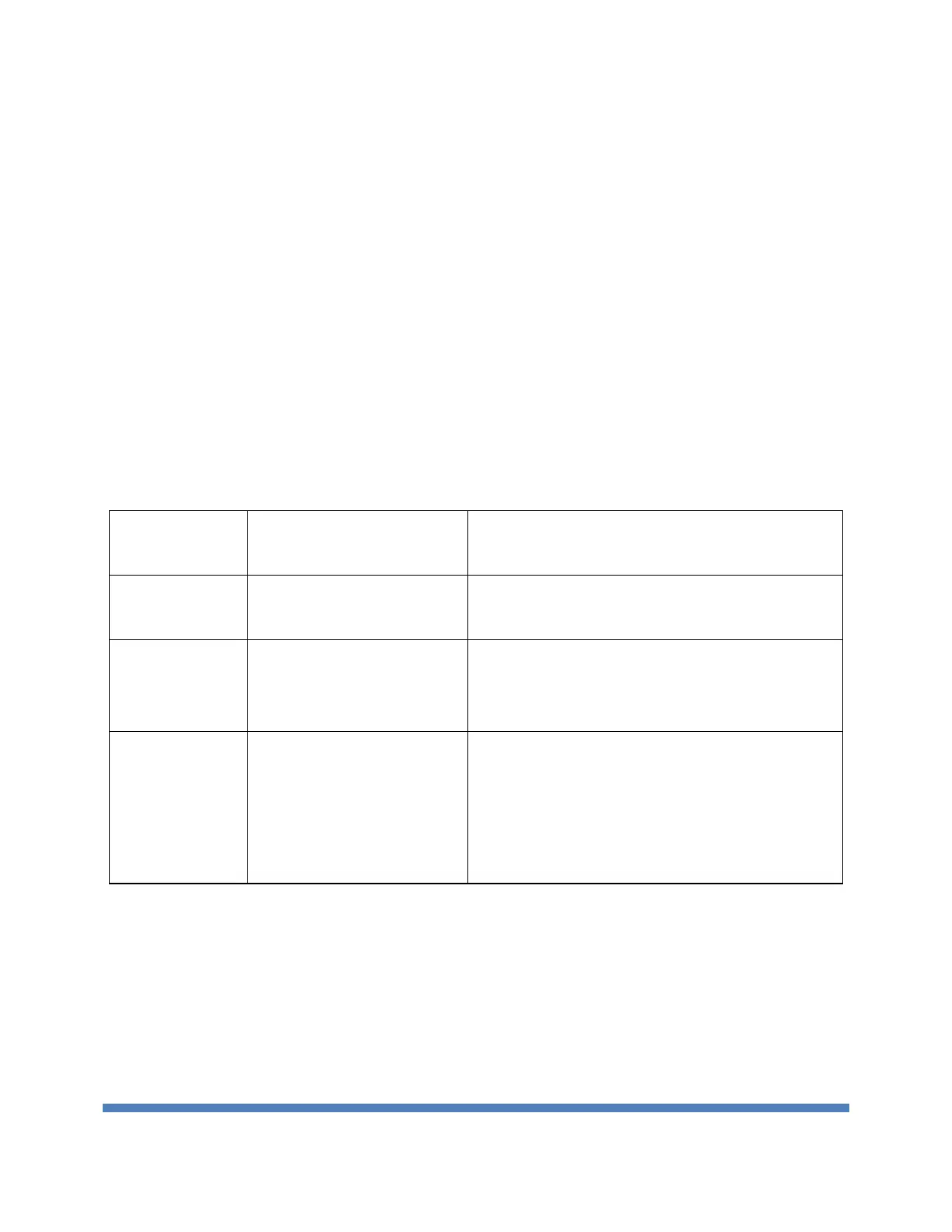

Table 38 IDT 8V89307 Configurations

5.13.2. POR of IDT 8V89307

The detailed power-on reset (POR) flow is as follows:

1. 3.3V up and Ref clock up

2. Then 3.3V enable MPS1482 to generate 1.8V

3. All power are stable, POWR607 inform CPLD

4. CPLD receive the signal, CPLD assert Reset_N high

Loading...

Loading...