EDGECORE NETWORKS CORPORATION 2018

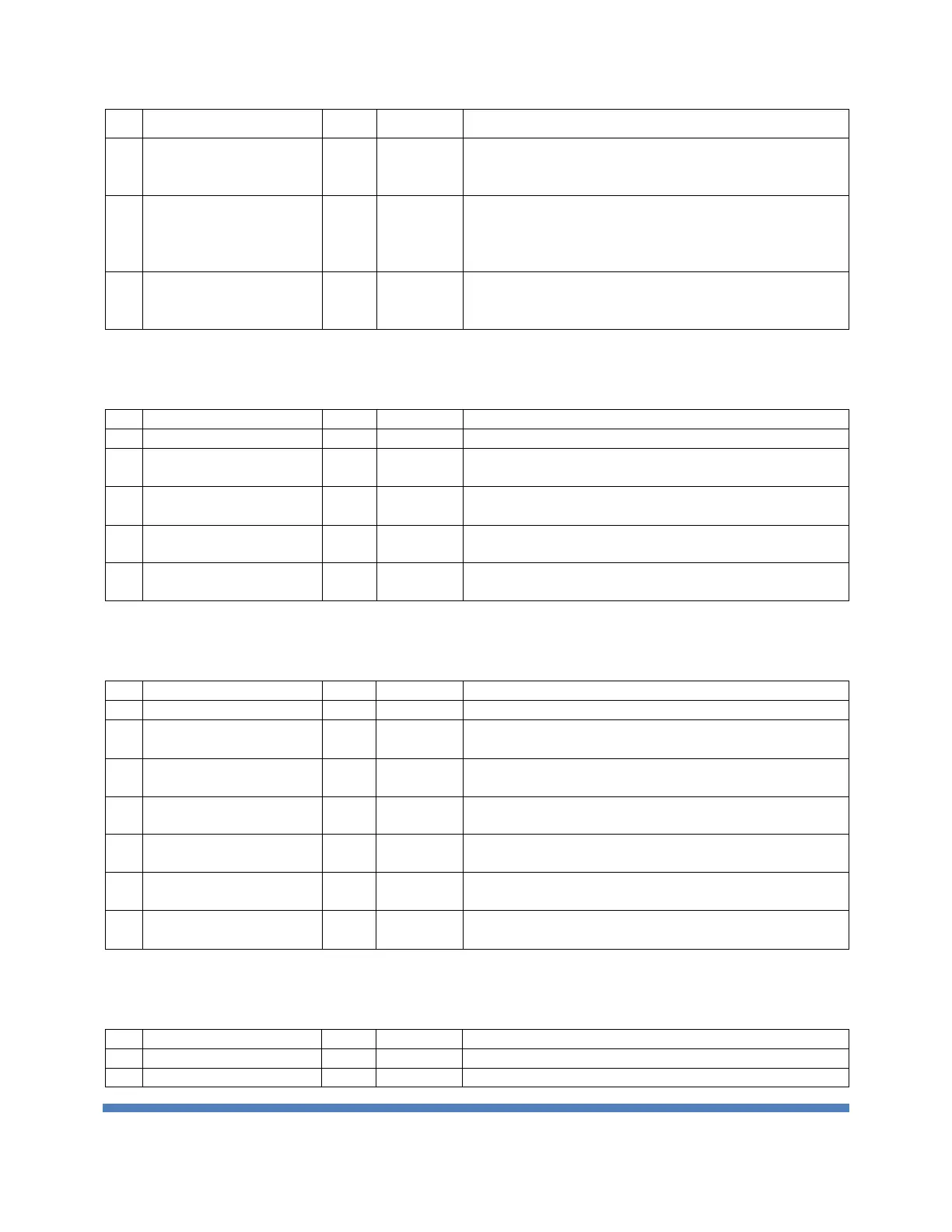

0: system would enter sleep mode

1: system is work at S0 state

0: system would be reset

1: system is work at S0 state

0: all power on the board would be powered off except

standby voltage.

1: system is work at S0 state

0: system will go to G3 state and wait for 10s, then go to S0.

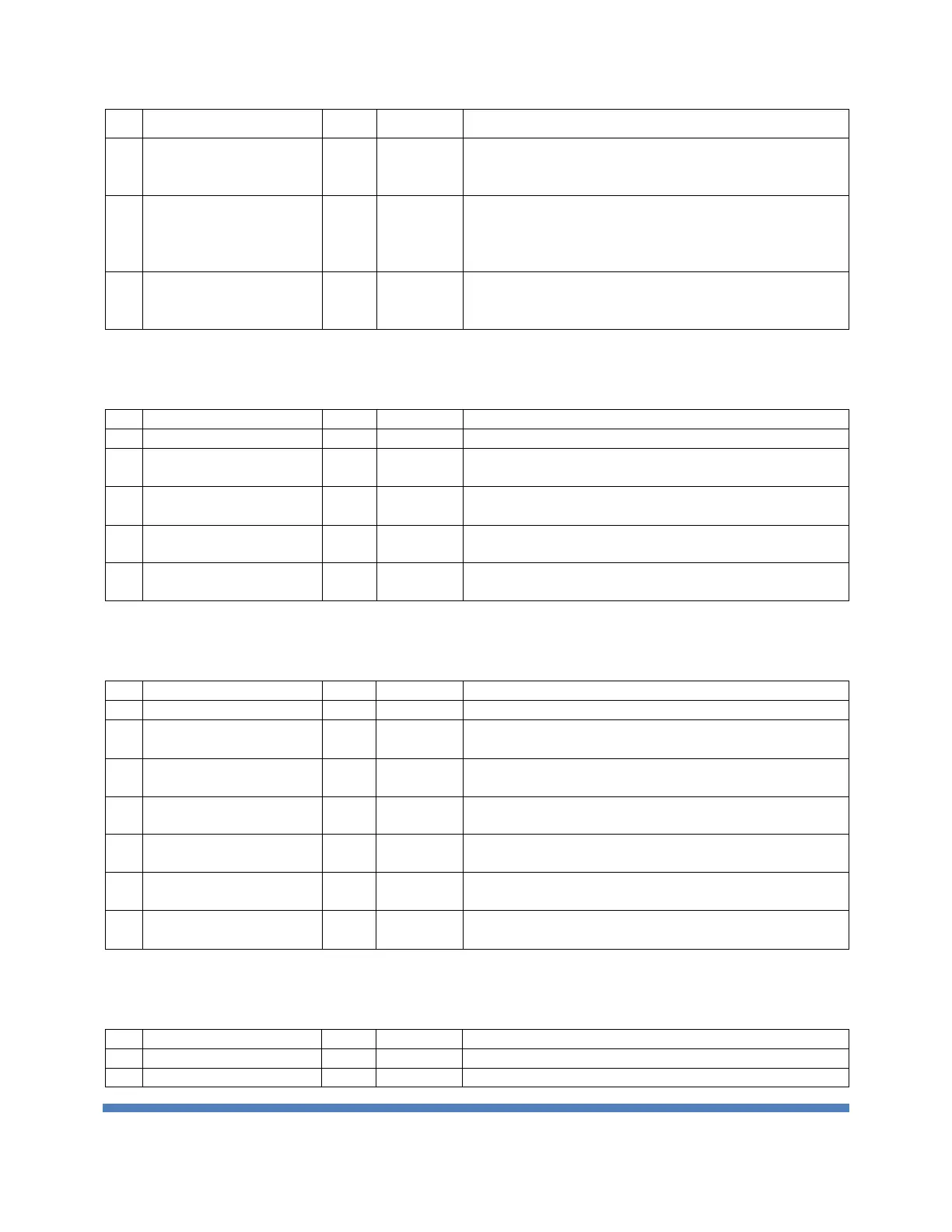

3.14.5. Offset 0x04 Reset - Device (Read& Write)

1: TPM Module is placed in normal operation state.

0: TPM Module is placed in reset state.

1: PCA9548 is placed in normal operation state.

0: PCA9548 is placed in reset state.

1: BCM5720 is placed in normal operation state.

0: BCM5720 is placed in reset state.

1: Main board in normal operation state.

0: Main board is placed in reset state.

3.14.6. Offset 0x05 System Interrupt (Read& Write)

1: No interrupt from LM75 (0x4B)

0: Interrupt from LM75 (0x4B)

1: No NMI event from BMC

0: BMC has NMI event

1: No interrupt event from the CPLD2, CPLD3 on MB

0: MB CPLD2, CPLD3 have interrupt events

1: No interrupt event from the CPLD1 on MB

0: MB CPLD1 has interrupt event

1: transceiver is placed in normal operation state.

0: transceiver is placed in reset state.

1: CPU is in normal operation state

0: CPU is in SMI event state

3.14.7. Offset 0x06 System Error (Read& Write)

1: transceiver is placed in normal operation state.

Loading...

Loading...