3.13.7. Thermal

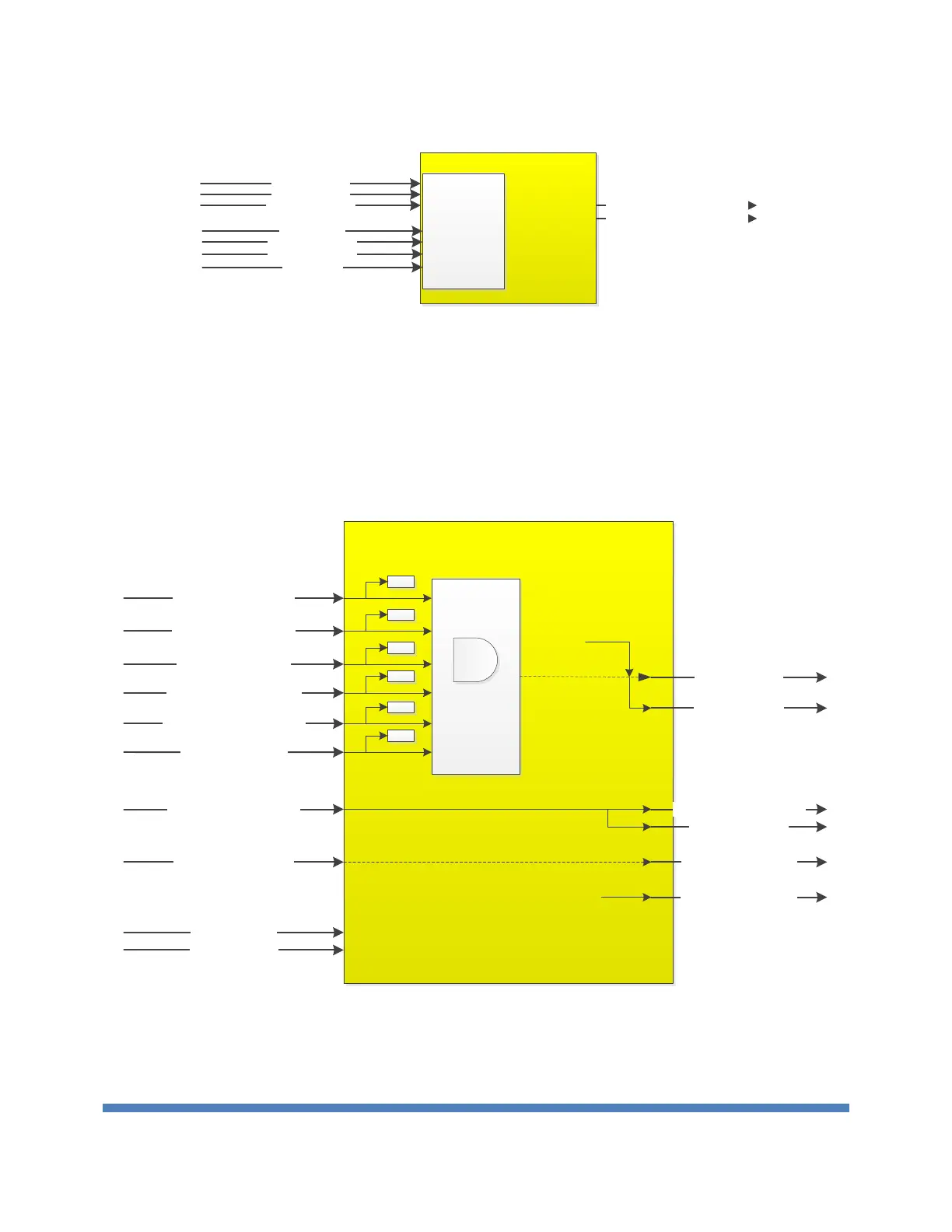

The thermal block is used to monitor the thermal event driven from CPU by

“CPLD_CPU_PROCHOT_N” / “CPLD_DDR01_MEMHOT”, “VR_PVCCIN_VRHOT_N” / ”

VR_P1V05_PCH_VRHOT_N” / ” P1V2_VDDQ_IRQ_VRHOT_N” from VRs, and “CPLD_DDR_EVENT_N”

from DDR memory, then use “CPLD_PCHHOT_N” and “B2B_PROCHOT_N” to announce PCH and MB.

“CPLD_CPU_THERMTRIP_N” is driven from CPU to indicate THERMTRIP event then use

“CPLD_PCH_THERMTRIP_N” and “B2B_THERMTRIP_N” to announce PCH and MB

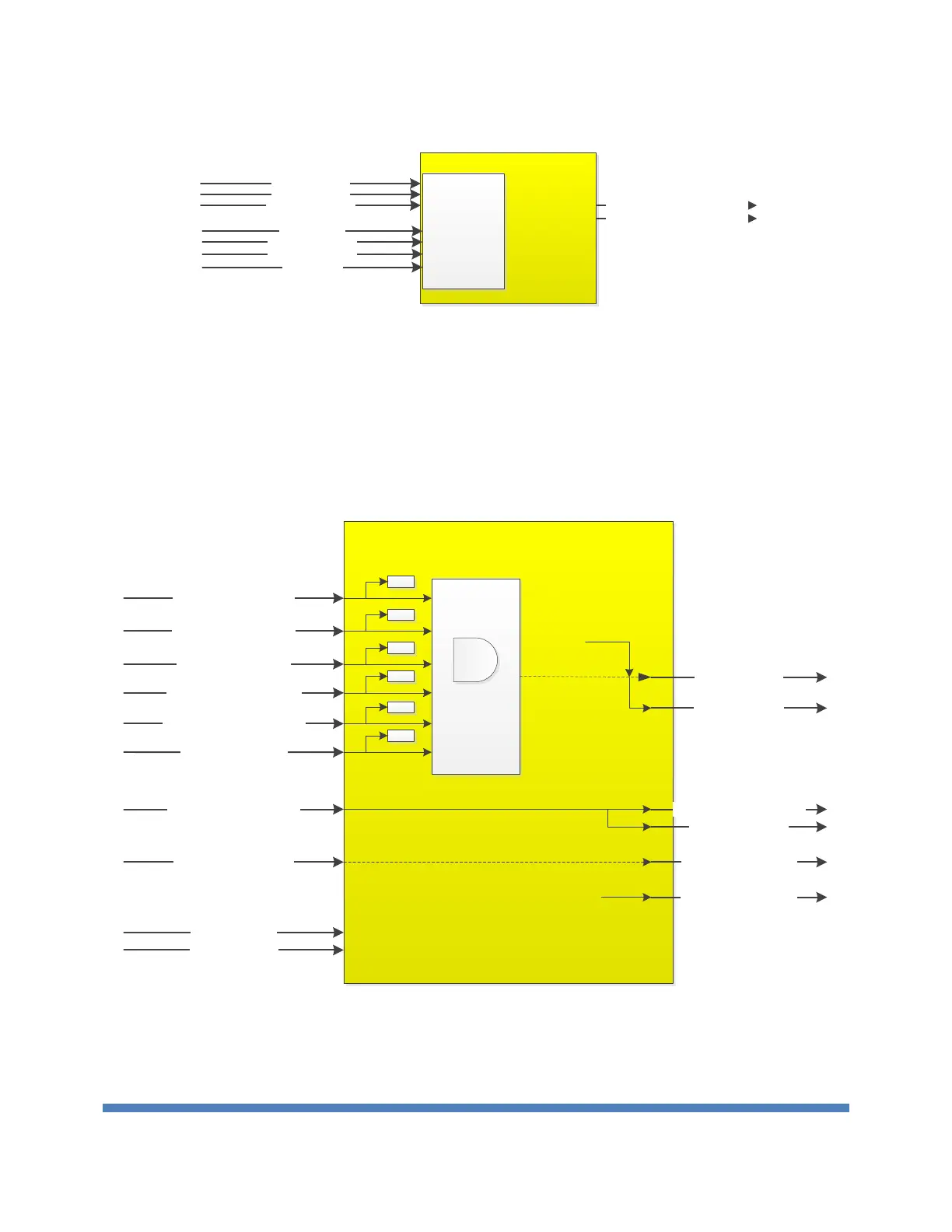

Figure 28 CPLD Thermal Diagram

Loading...

Loading...