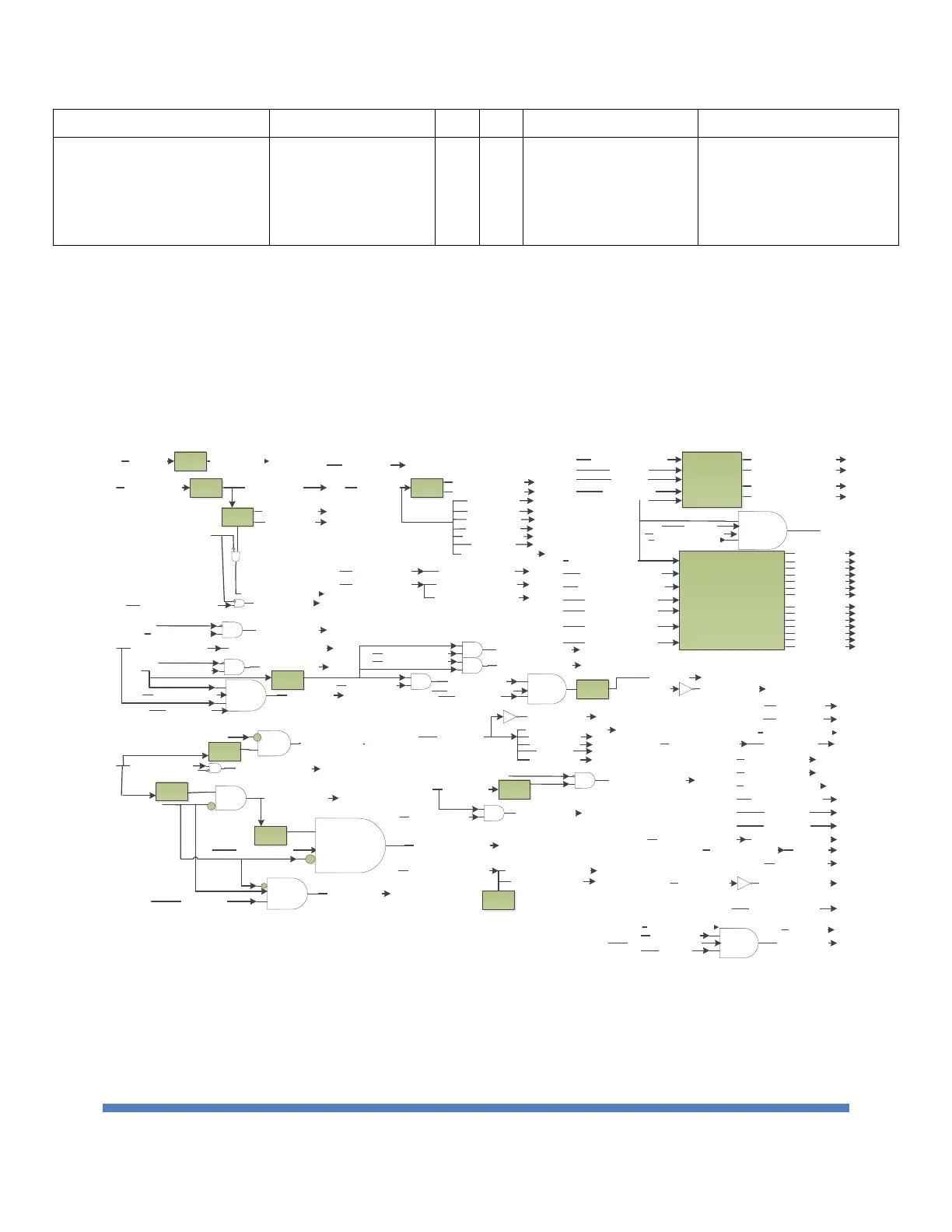

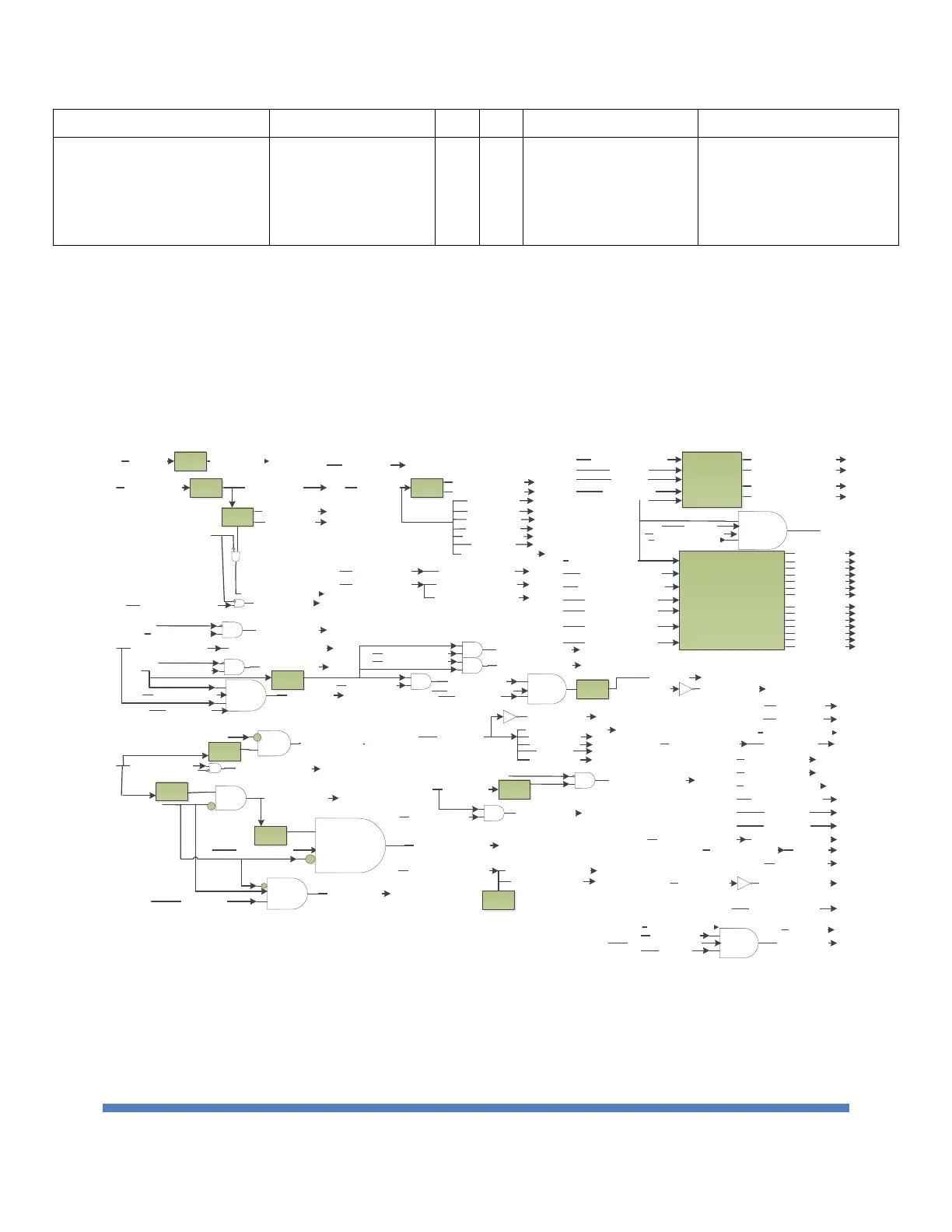

3.12. CPLD (For CPU Board)

The aim of the CPLD on the BDXDE CPU Board in the ES7654NT chassis is major for

power sequence, reset system, system interrupt, and BMC module function support.

The I2C address info of the CPLD is 0x65.

The CPLD has registers to record the board status, including error function , power

status , interrupt event , thermal event from CPU , and also the board ID and CPLD version.

Figure 24 CPLD block diagram

Loading...

Loading...