EDGECORE NETWORKS CORPORATION 2018

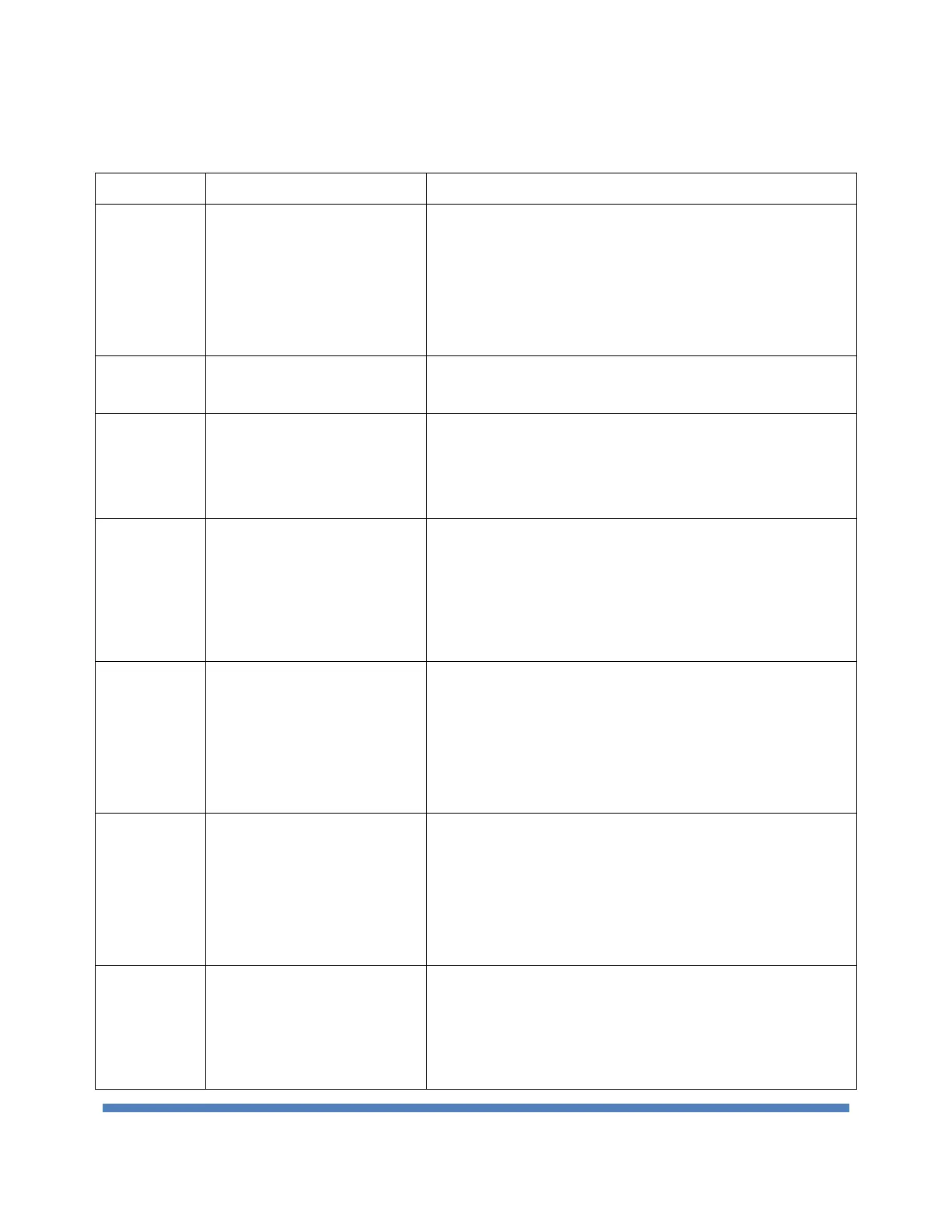

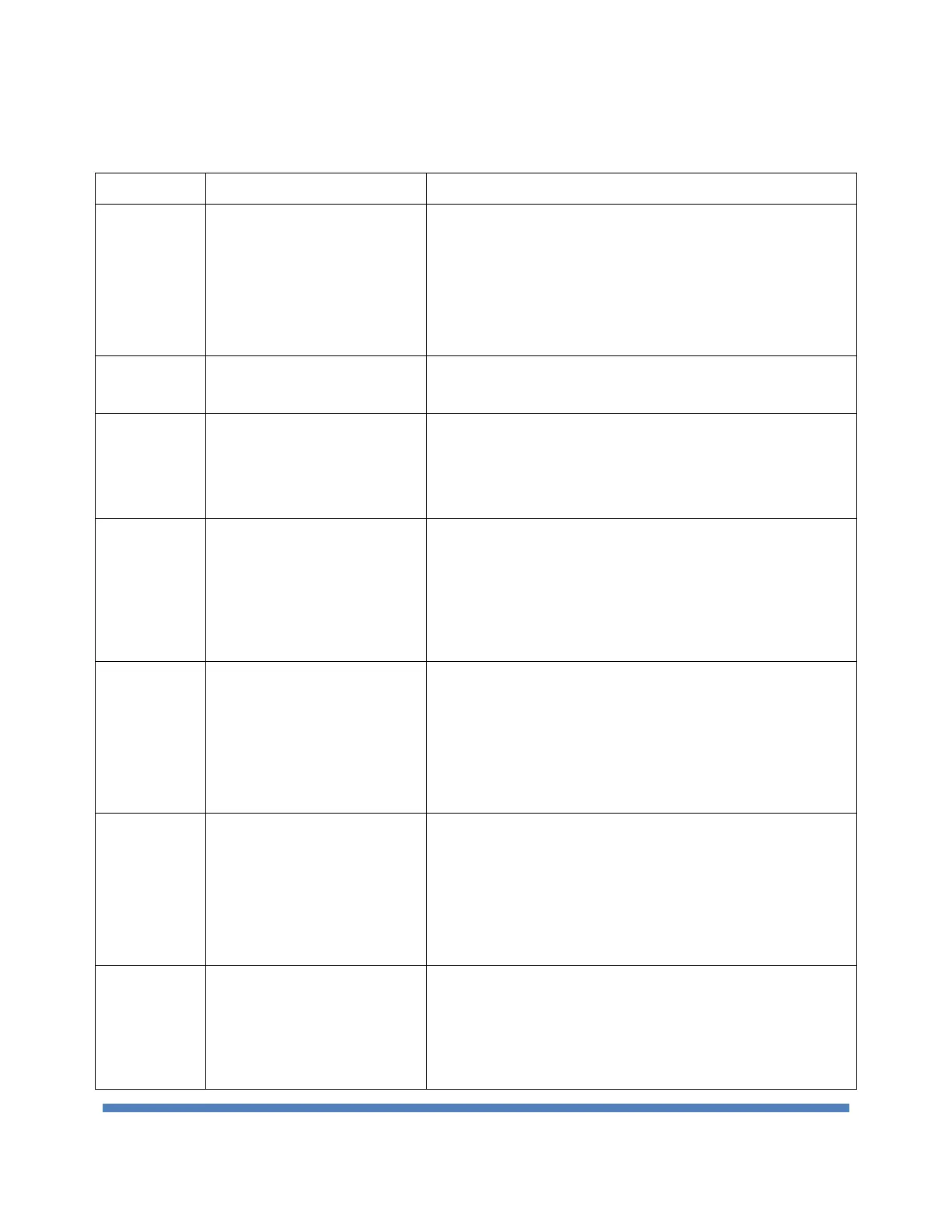

4.1. Configurations of MAC (BCM56873)

Table 16 MAC Configurations Table

Selects the boot flow for mHost0 (the first internal ARM R5):

3’b000: Load all necessary code from QSPI flash attached to

IP_QSPI interface and begin execution.

(others): Reserved

Note: These signals have no effect if MHOST0_BOOT_DEV is

pulled low

Selects the lower two bits of the BSC slave address used on

the BSC2 interface.

Selects the operating mode of the QSPI flash device connected

to the IP_QSPI interface:

1’b0= QSPI flash is operating in 3 byte address mode

1’b1= QSPI flash is operating in 4 byte address mode

Selects the mode that is used for sending commands and

addresses to the QSPI flash device connected to the IP_QSPI

interface:

1’b0: Commands and addresses are sent serially, data is sent

in parallel

1’b1: Commands, addresses, and data are sent in parallel

Selects the IP_QSPI interface’s operating mode:

1’b0: IP_QSPI interface operates using a serial interface

1’b1: IP_QSPI interface operates using a two bit parallel

interface

Note: If this signal is pulled high, the IP_QSPI_QUAD_LANE

signal must be pulled low

Selects the IP_QSPI interface’s operating mode:

1’b0: IP_QSPI interface operates using a serial interface

1’b1: IP_QSPI interface operates using a four bit parallel

interface

Note: If this signal is pulled high, the IP_QSPI_DUAL_LANE

signal must be pulled low

Selects the way that mHost0 (the first internal ARM R5) is

brought out of reset:

1’b0: mHost0 is held in reset

1’b1: mHost0 comes out of reset and begins executing code

based on the setting of the BOOT_DEV[2:0] strap signals

Loading...

Loading...