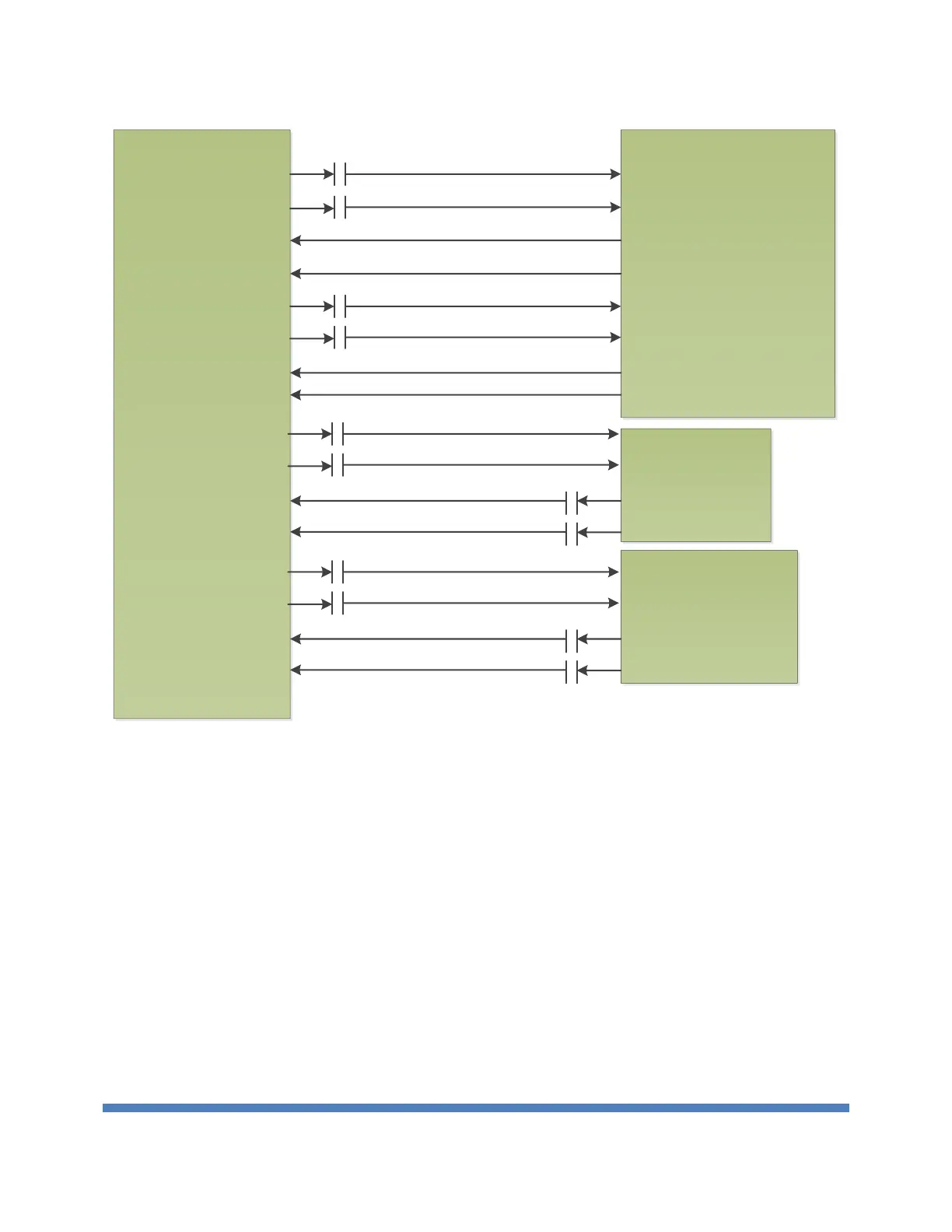

BDXDE

PE1_TX_DN[3:0]

PE1_TX_DP[3:0]

PCIE2_TX_DN[6]

PCIE2_TX_DP[6]

PE1_RX_DN[3:0]

PE1_RX_DP[3:0]

PCIE2_RX_DP[6]

PCIE2_RX_DN[6]

BCM5720

PCIE2_TX_DN[0:1]

PCIE2_TX_DP[0:1]

PCIE2_RX_DP[0:1]

PCIE2_RX_DN[0:1]

PCIE_OOB_RX_N

PCIE_OOB_RX_P

PCIE_OOB_TX_N

PCIE_OOB_TX_P

CPU_PEX_PCIE[B:A]_TX_[1:0]_P

CPU_PEX_PCIE[B:A]_TX_[1:0]_N

CPU_PEX_PCIE[B:A]_RX_[1:0]_P

CPU_PEX_PCIE[B:A]_RX_[1:0]_N

120pins BTB connector

PE_TP

PE_TN

PE_RP

PE_RN

BMM

PCIE2_TX_DN[5]

PCIE2_TX_DP[5]

PCIE2_RX_DP[5]

PCIE2_RX_DN[5]

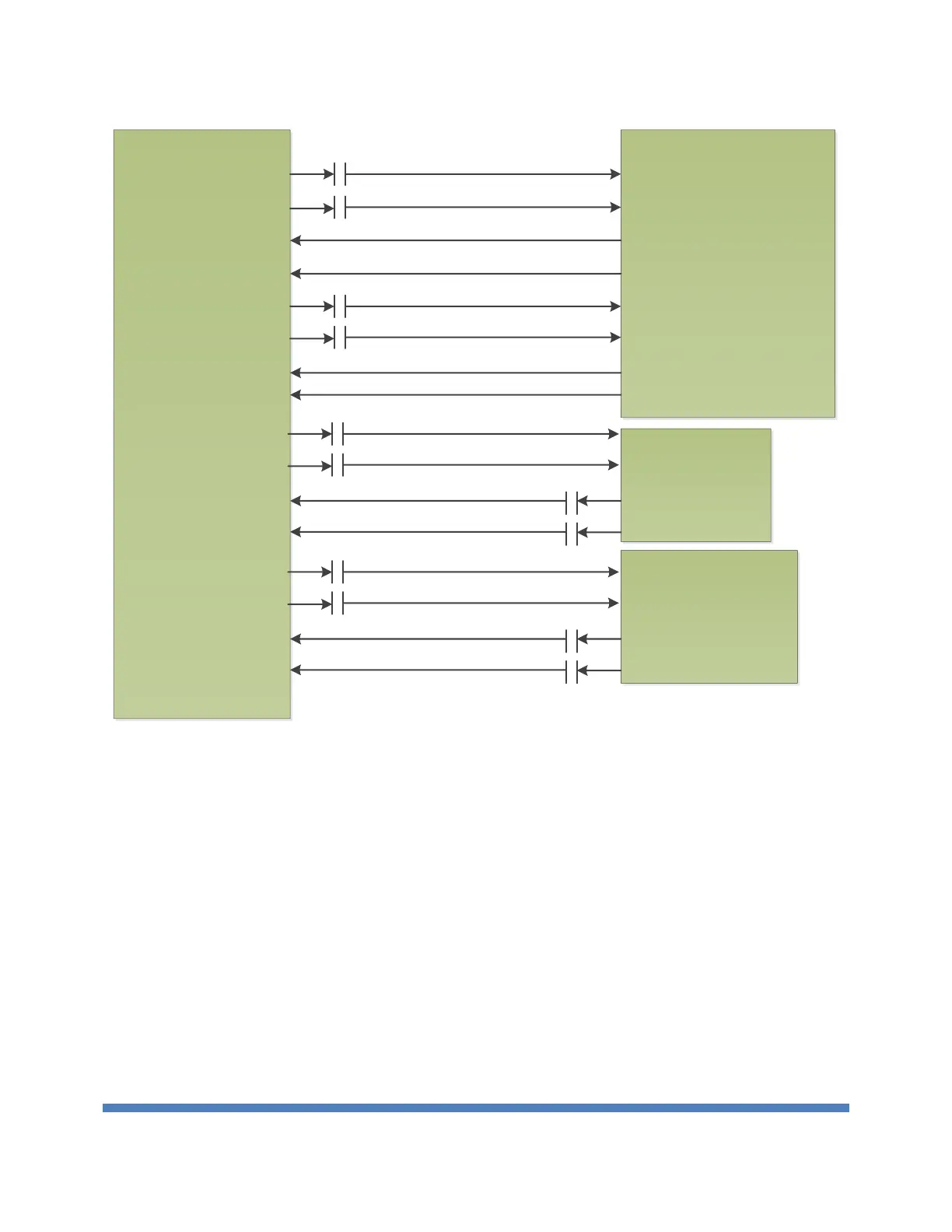

3.8. I2C/SMBus Architecture

The SMbus from Broadwell-DE can access the CPU board and main board device via SMBUS0.

The multiplexers(MUX) are used to prevent multi-master issues on the SMBUS.

The BMC module could use the SMBUS when the I2C_multiplexer_select pin is driven from high to low.

In order to prevent the hang-up issue which occurred when the CPU is accessing the SMBUS and BMC

module want to take the bus master (I2C_multiplexer_select would be driven low), if the BMC module

is installed, BMC would be the master for all SMBUS, CPU would ask BMC for SMBUS information via

LPC by IPMI.

Figure 19 I2C Connection

Loading...

Loading...