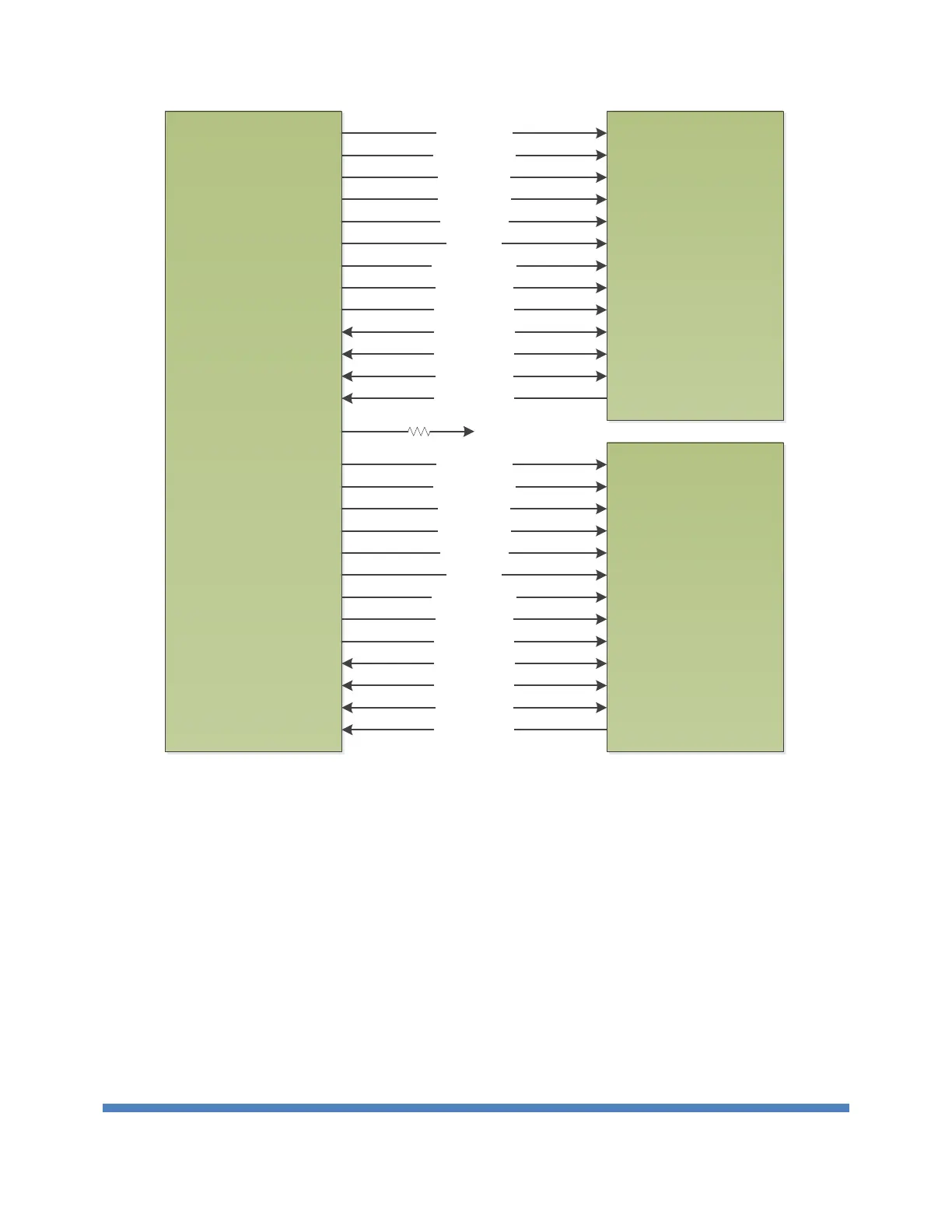

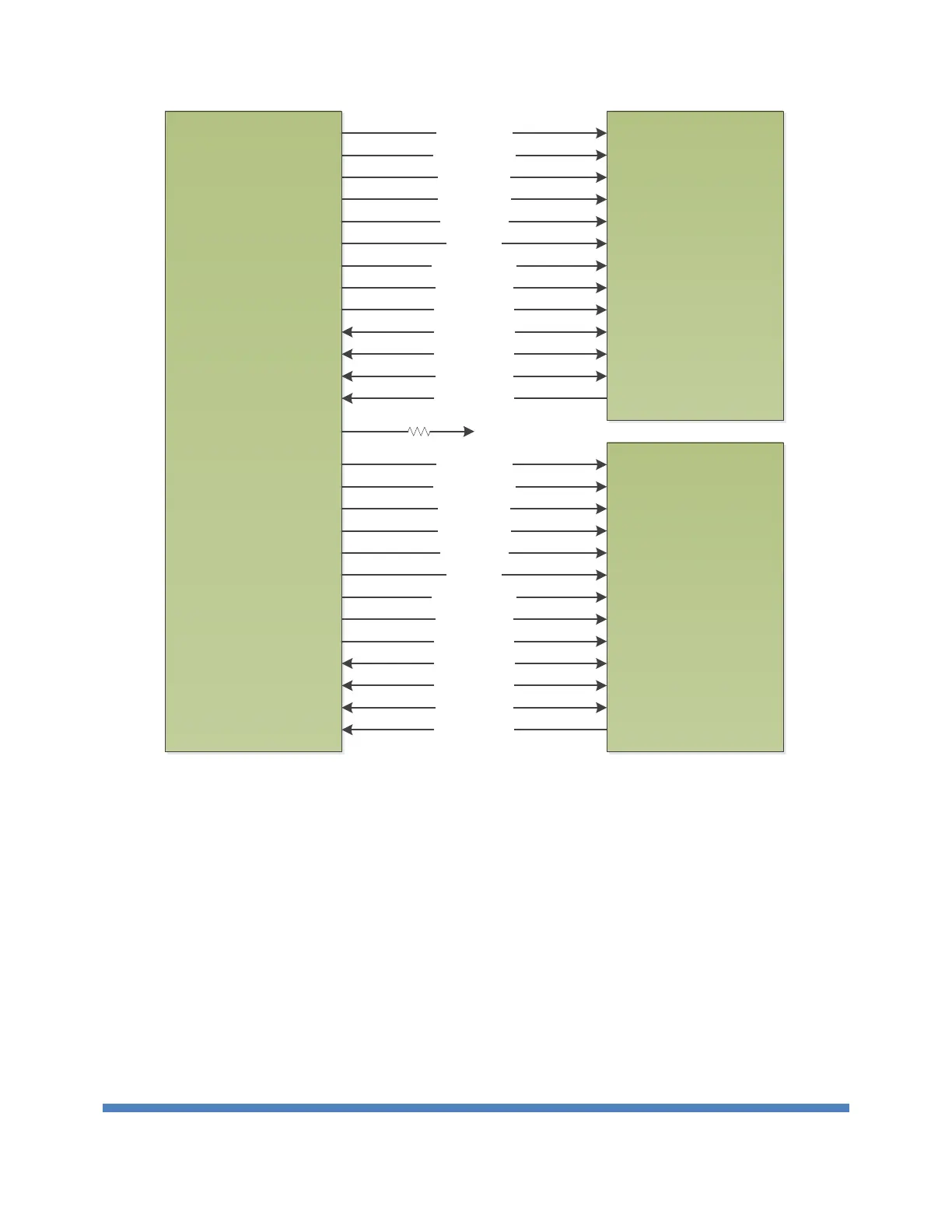

3.7. PCIe

The CPU board has to provide the x4 PCIE Gen3 and x1 PCIE Gen2 to main board. The x4 PCIE GEN3 is

used to connect the NP8365 for control path, the PCIE GEN2 x1 is sued to communicate the OOB.

There are other PCIE GEN2 that connect to on board MAC BCM5720 and BMC module.

The PCIE interface connected to BCM5720 is PCIE GEN2 x2.

The PCIE interface connected to BMC module is PCIE GEN2 x1, which is used to active the graphic

inside the BMC chip to achieve the vKVM and vMedia function through IPMI when the BMC chip uses

AST2400.

Figure 18 PCIe Connection

Loading...

Loading...