Multifunction Electrical Tester Calibrator

Supported SCPI Commands

153

ESR Event Status Register

Every bit of the EventStatusRegister corresponds to one event. Bit is set when

the event is changed and it remains set also when the event passed. The ESR is

cleared when the power is turned on (except bit PON which is set), and every

time it is read via command *ESR? Or cleared with *CLS. See Table 19.

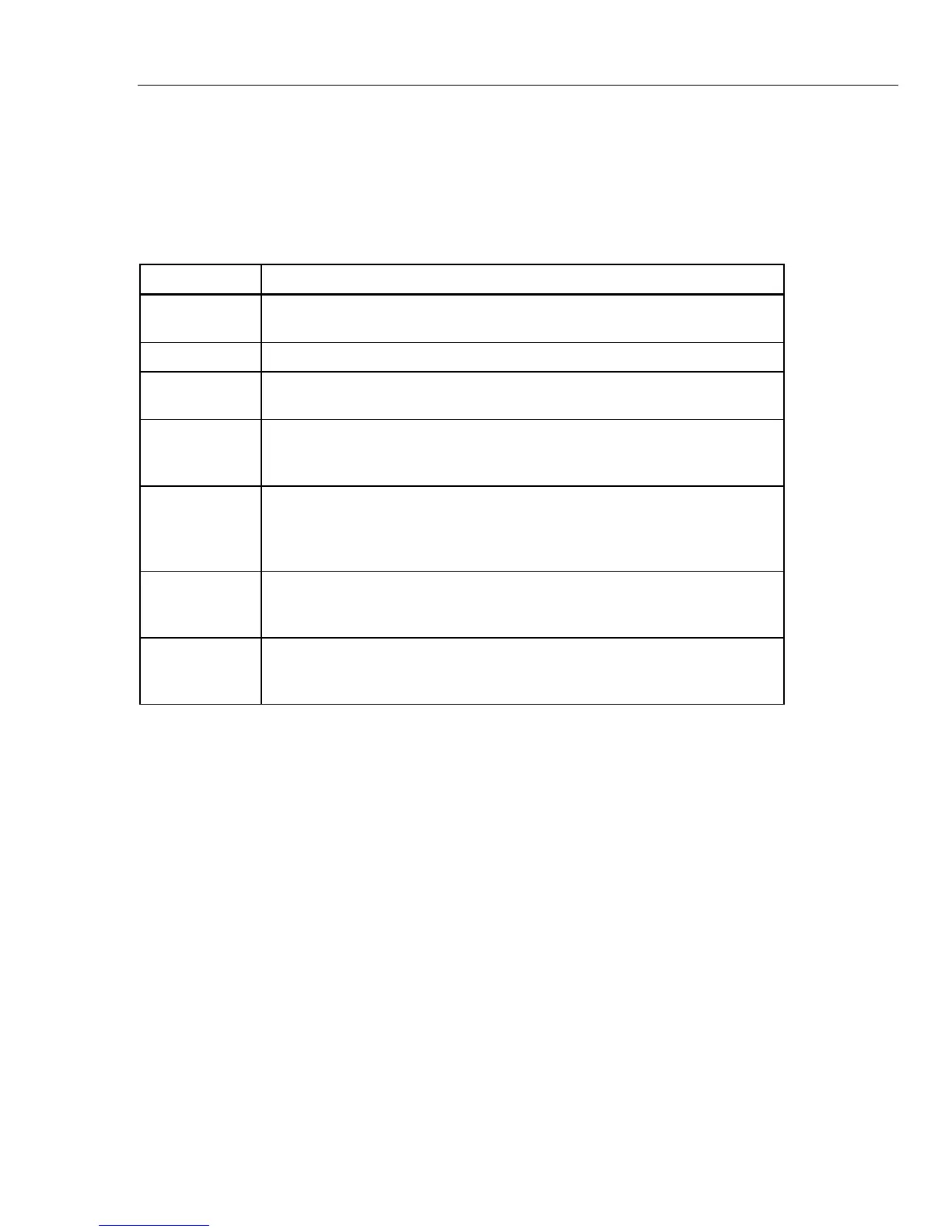

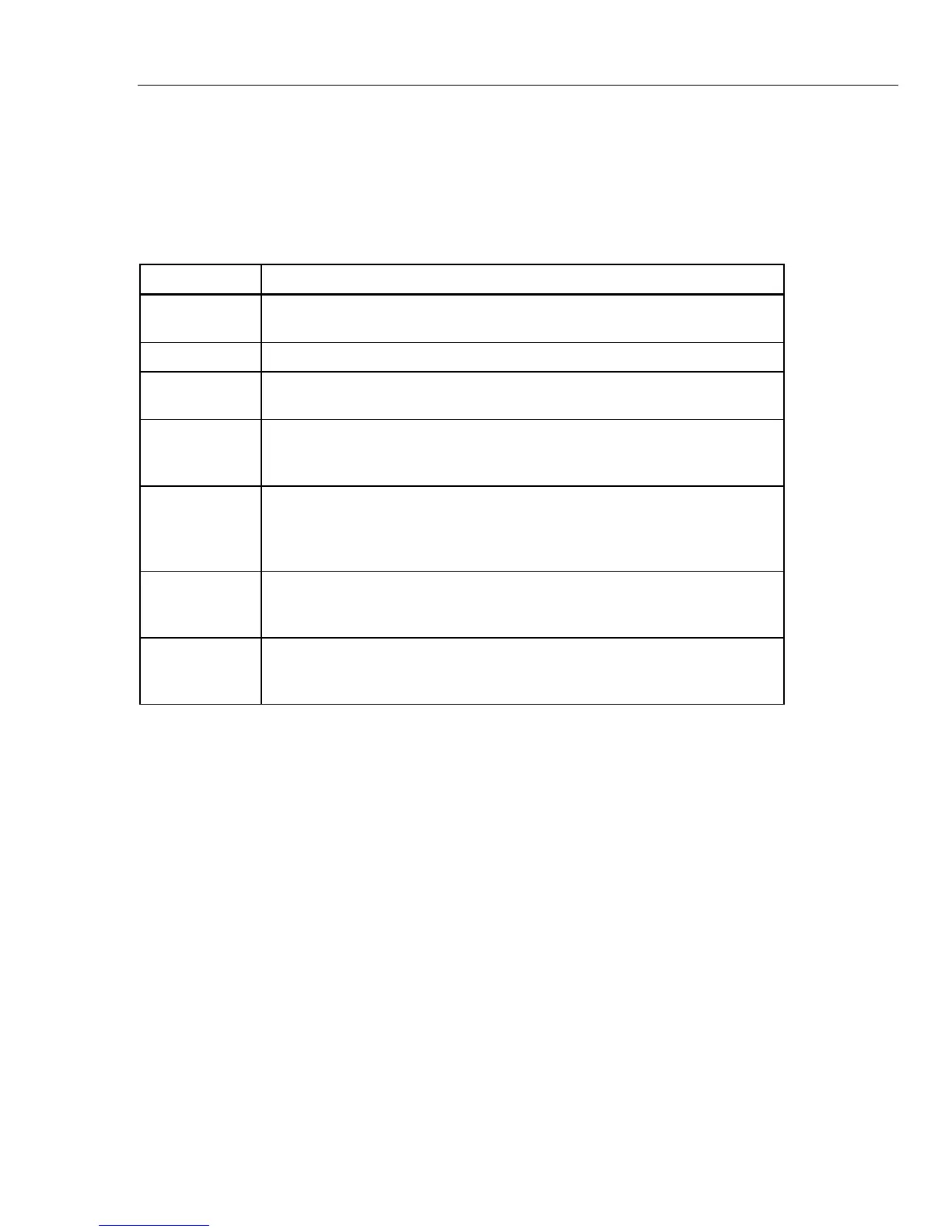

Table 19. Bit Configuration of the Event Status Register

Bit Name Event Description

PON

Power On, bit 7. This event bit indicates that an off-to-on transition has occurred in

the Product power supply.

URQ User Request, bit 6. Bit is not used and it is always 0.

CME

Command Error, bit 5. This event bit indicates that an incorrectly formed command

or query has been detected by the Product.

EXE

Execution Error, bit 4. This event bit indicates that the received command cannot

be executed, owing to the device state or the command parameter being out of

limits.

DDE

Device Dependent Error, bit 3. This event bit indicates that an error has occurred

which is neither a Command Error, a Query Error, nor an Execution Error. A

Device-specific Error is any executed device operation that did not properly

complete due to some condition, such as overload.

QYE

Query Error, bit 2. The bit is set if the Product is addressed as talker and output

queue is empty or if control unit did not pick up response before sending next

query.

OPC

Operation Complete, bit 0. This event bit is generated in response to the *OPC

command. It indicates that the device has completed all selected pending

operations.

ESE Event Status Enable Register

The Event Status Enable Register allows one or more events in the Event Status

Register to be reflected in the ESB summary-message bit. This register is

defined for 8 bits, each corresponding to the bits in the Event Status Register.

The Event Status Enable Register is read with the common query *ESE?. Data is

returned as a binary-weighted value. The Event Status Enable Register is written

to by the common command, *ESE. Sending the *ESE common command

followed by a zero clears the ESE. The Event Status Enable Register is cleared

upon power-on.

It suppresses or allows bits in the ESR register. Value 0 of a bit of ESE register

suppresses influence of appropriate bit of ESR register on value of sum bit of

ESB status register. Setting of any unmask bit of ESR register results in setting

of ESB status register. ESE register value can be modified by command *ESE

followed by value of mask register (integer in range 0–255). Reading of the

register can be performed with command *ESE?. The register is automatically

reset after switching on. The register is not reset with *CLS command.

Loading...

Loading...