MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

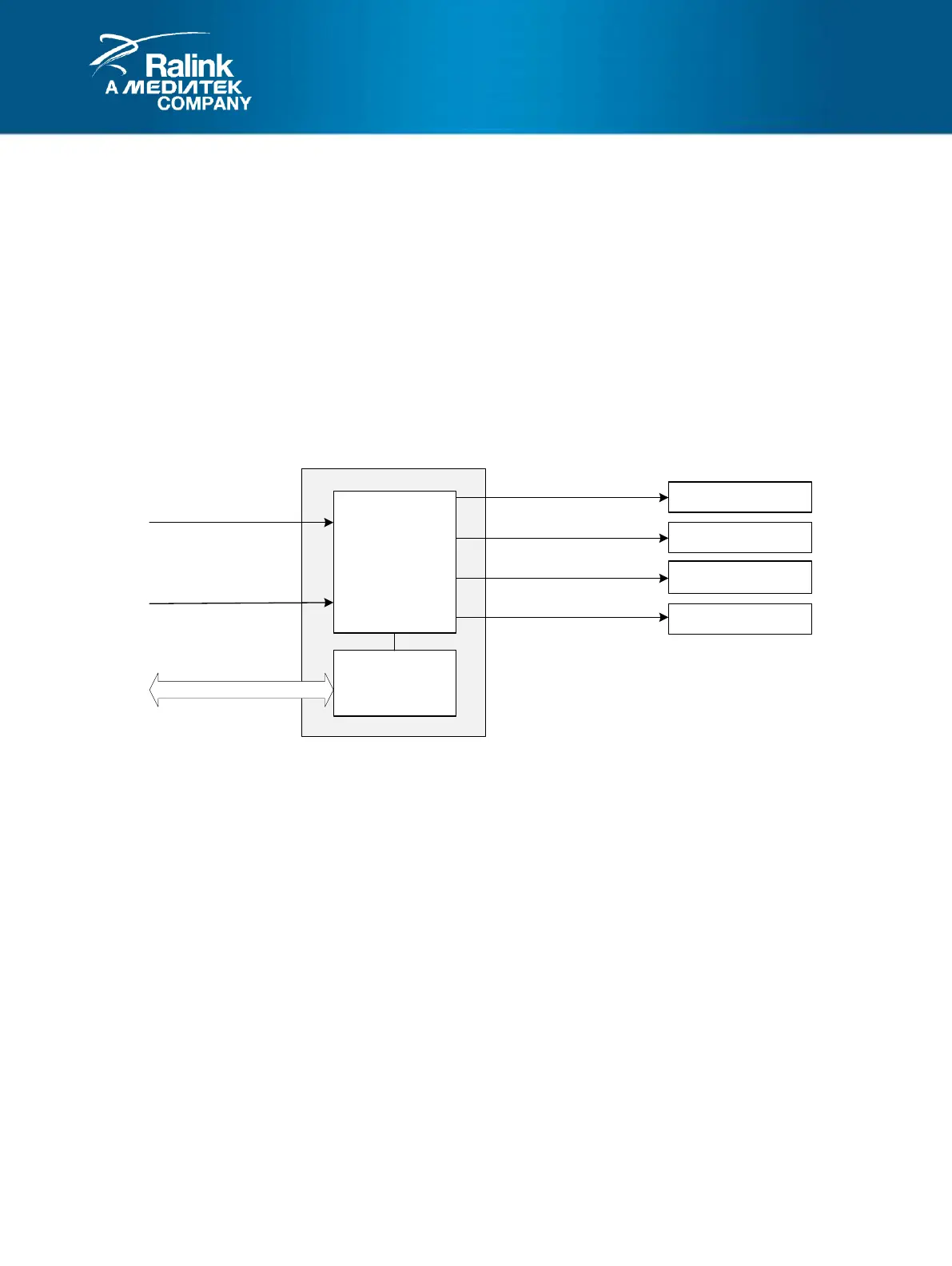

2.2 System Control

2.2.1 Features

Provides read-only chip revision registers

Provides a window to access boot-strapping signals

Supports memory remapping configurations

Supports software reset to each platform building block

Provides registers to determine GPIO and other peripheral pin muxing schemes

Provides some power-on-reset only test registers for software programmers

Combines miscellaneous registers (such as clock skew control, status register, memo registers, etc)

2.2.2 Block Diagram

System Control

Registers

PalmBus Interface

System Control Block

CPU Rbus Wrapper

Pin Muxing Block

Platform Blocks

PCIe, PCM, ...

Boot Strapping Signals

Cache Hit/Miss Strobes

To/From MIPS

Memory Remapping

GPIO Pin Muxing Scheme

Per Block S/W Reset

Miscellaneous Registers

Figure 2-1 System Control Block Diagram

Loading...

Loading...