MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.20.6.3 ACL Rule Control

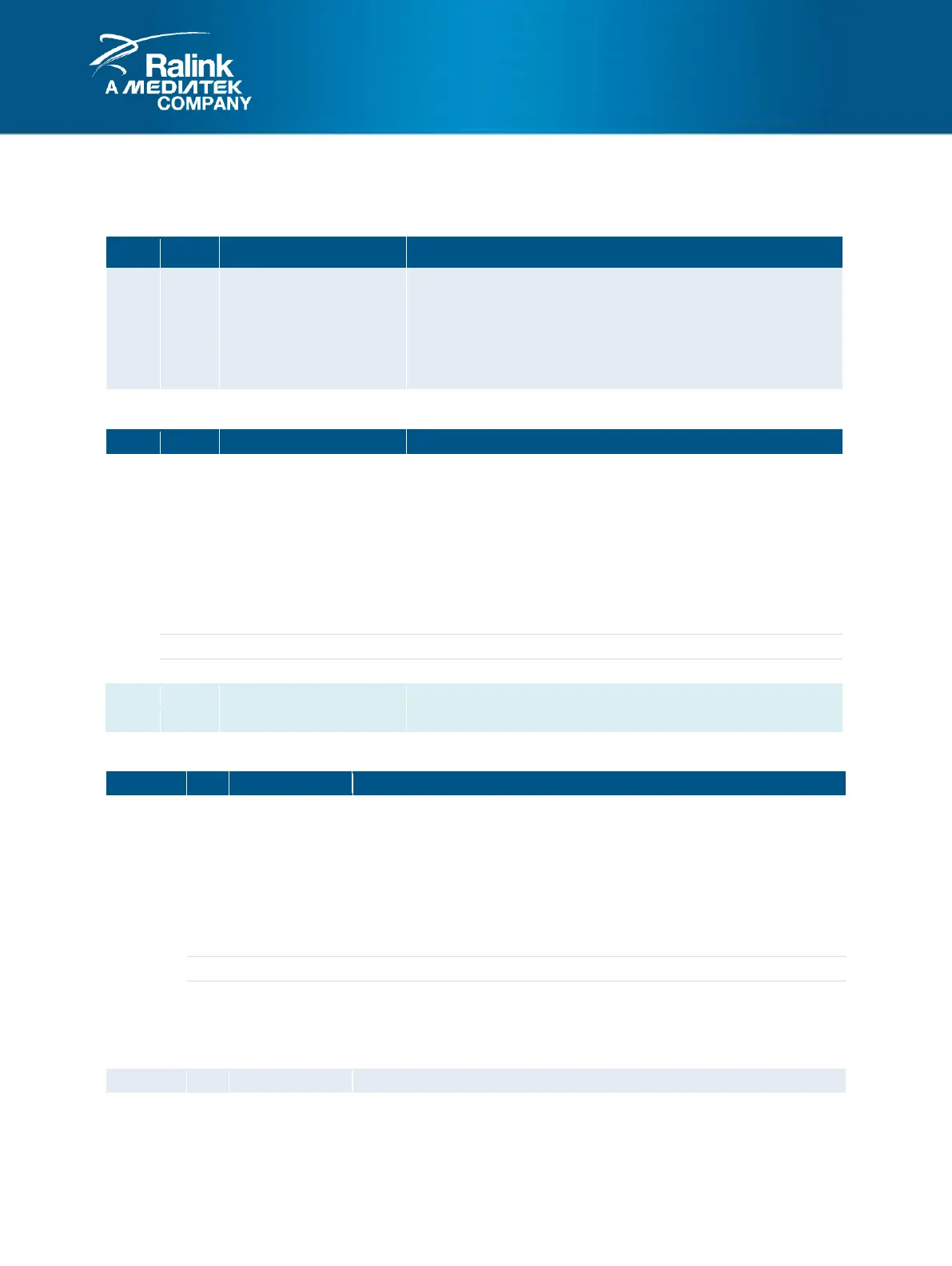

Table 2-3 Rule Mask

Hit Pattern

When a valid bit is set in this table, it means that the

corresponding pattern in the rule table must be hit and

necessary.

If all the valid bits can be found in the rule flag, then the rule

control can be applied on this packet.

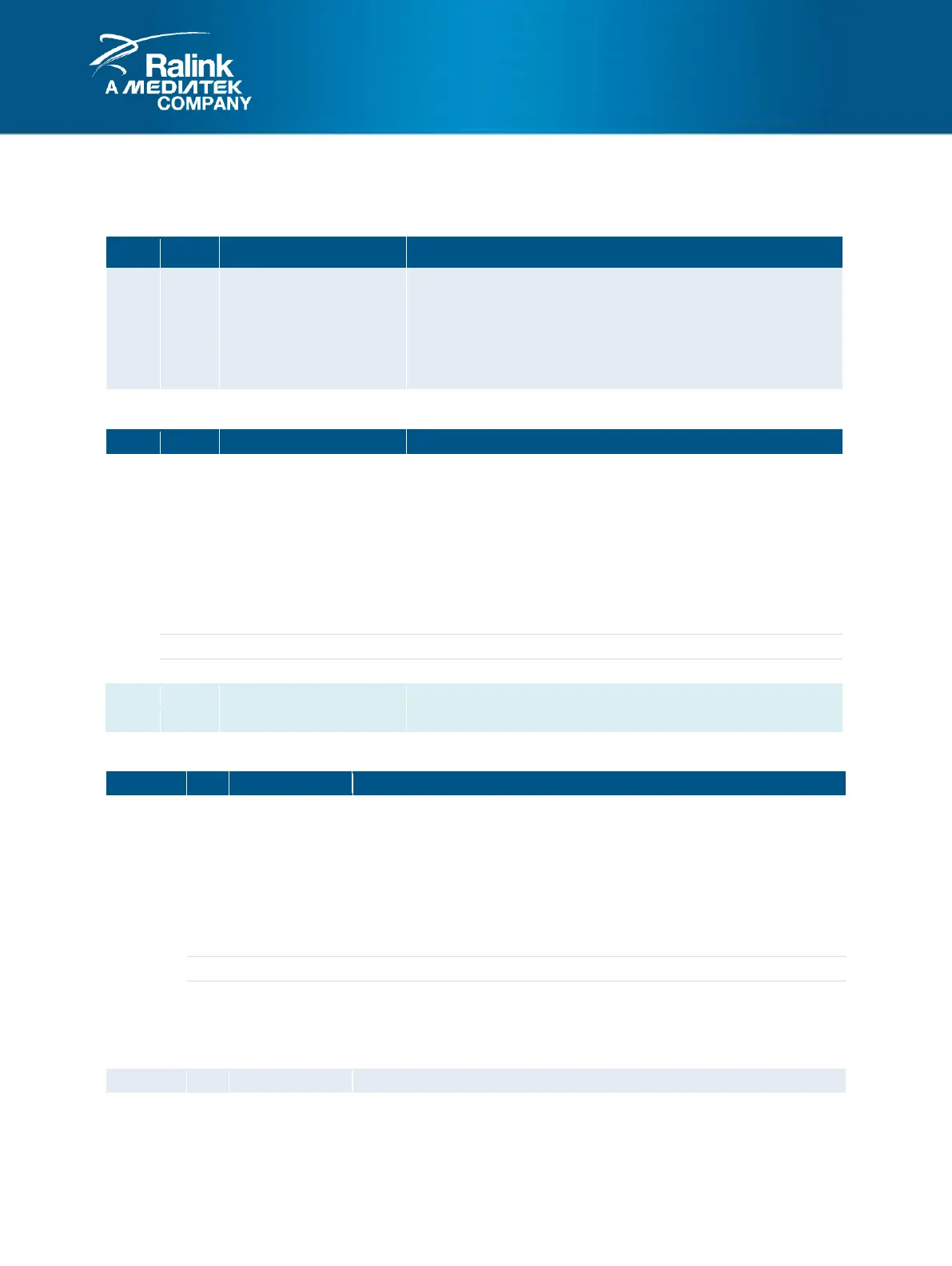

Table 2-4 Rate Control

Per Flow Ingress Rate Limit Control

Per the rate limit, multiple rule controls can constrain one

packet. Generally, the minimum ingress rate will limit the flow

rate.

14’h0: 0 * 64 Kbps

14’h1: 1 * 64 Kbps

14’h2: 2 * 64 Kbps

…

14’h3D09: 15625 * 64 Kbps (1000 Mbps)

Per Flow Ingress Rate Limit Enable (Multi/First)

Per Flow Ingress Rate Limit Accumulator

Table 2-5 Rule Control

Frame TO_CPU Forwarding

3’b0xx: System Default (Disable)

3’b100: System Default and CPU Port Excluded

3’b101: System Default and CPU Port Included

3’b110: CPU Port Only (As long as the ingress port is not the CPU port. If

the ingress port is the CPU port, then the system default and CPU

port are excluded.)

3’b111: Frame Dropped

Frame Copy to Mirror Port

Force Destination Port Selection

1’b0: Destination port is based on ARL or register

1’b1: Destination port is based on PORT.

Destination Port Member / VLAN Port Member

Loading...

Loading...