MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

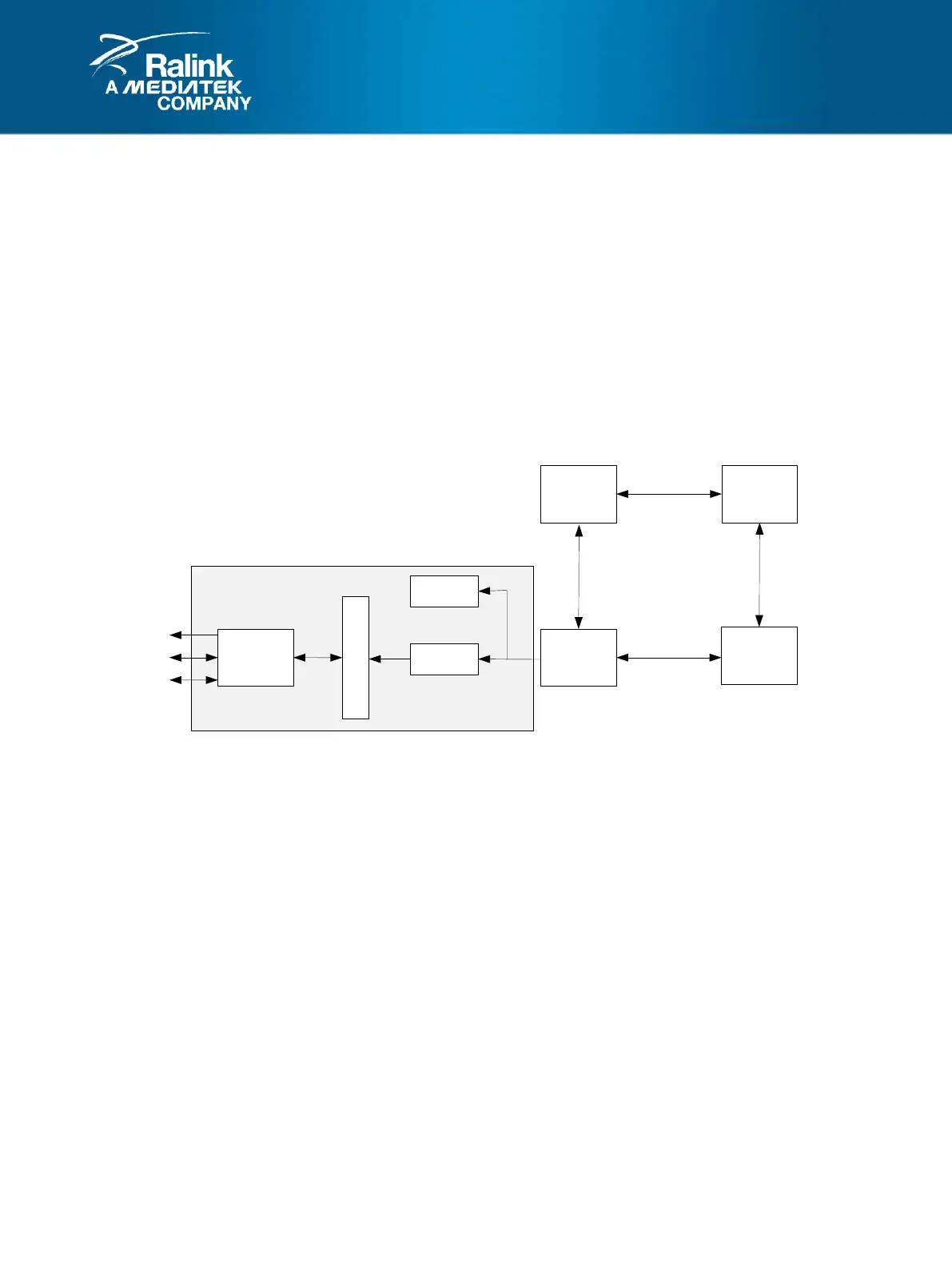

2.14 I2S Controller

2.14.1 Features

I2S transmitter/receiver, which can be configured as master or slave.

Supports 16-bit data, sampling rates of 8 kHz, 16 kHz, 22.05 kHz, 44.1 kHz, and 48 kHz

Support stereo audio data transfer.

32-byte FIFO are available for data transmission.

Supports GDMA access

Supports 12 Mhz bit clock from external source (when in slave mode)

2.14.2 Block Diagram

The I

2

S transmitter block diagram is shown as below.

FIFO

Async interface

RBUS

RBUS

RBUS

RBUS

PBUS

SD

WS

SCLK

I2S Design

CSR

CPU SDRAM

PBUS

Control

GDMA

Parallel-

to-serial

converter

Figure 2-14 I

2

S Transmitter Block Diagram

The I

2

S interface consists of two separate cores, a transmitter and a receiver. Both can operate in either master

or slave mode. The transmitter is only shown here in master or slave mode.

Loading...

Loading...