MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.5.2 Register Descriptions (base: 0x1000_0d00)

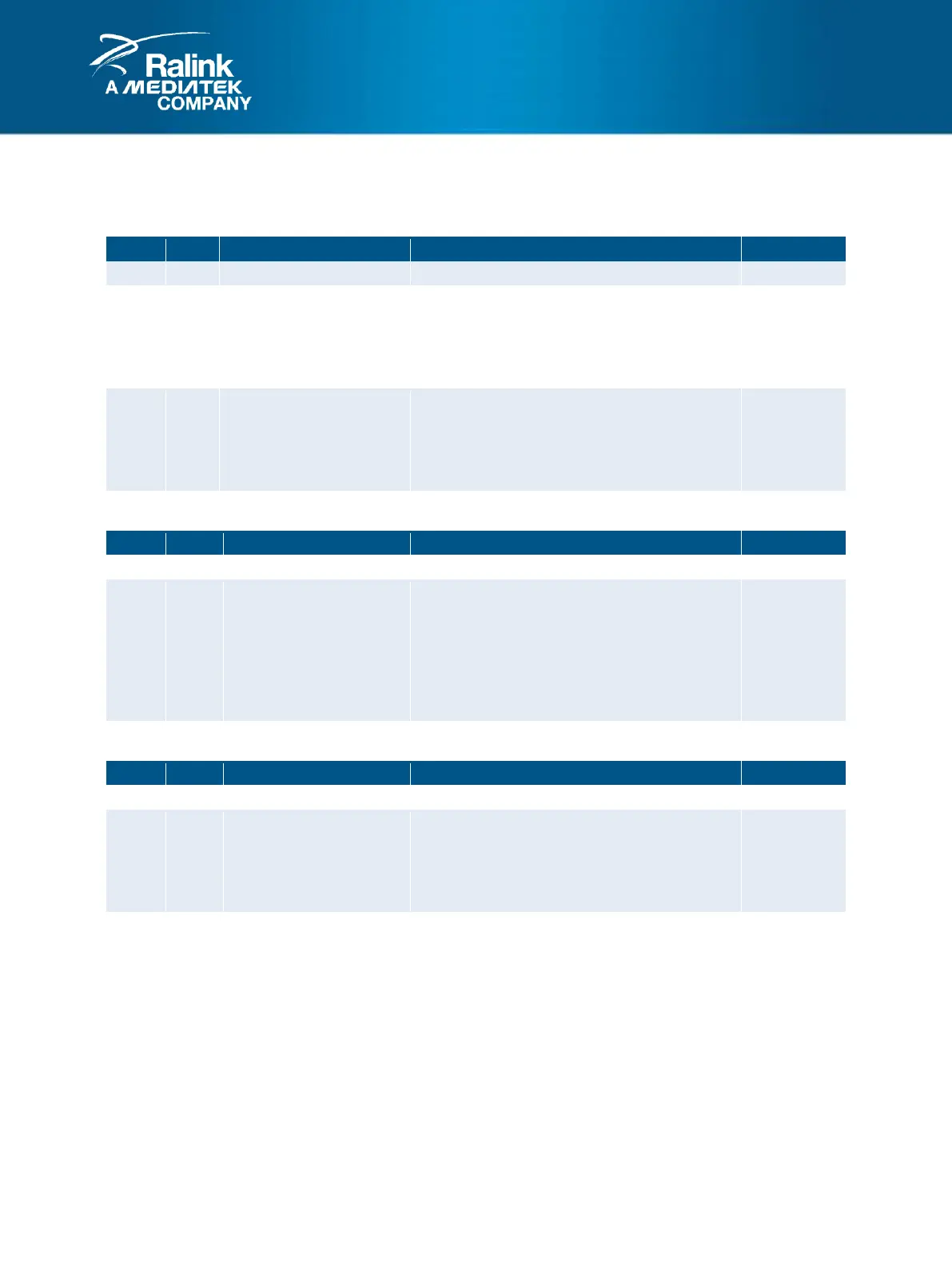

43. STCK_CNT_CFG: MIPS Configuration Register (offset: 0x0000)

External System Tick Enable

Selects the system tick source

0: Use the MIPS internal timer interrupt.

1: Use the external timer interrupt from an

external MIPS counter.

Count Enable

Enables the free run counter (MIPS counter).

This counter increments every 20 μs.

0: Disable

1: Enable

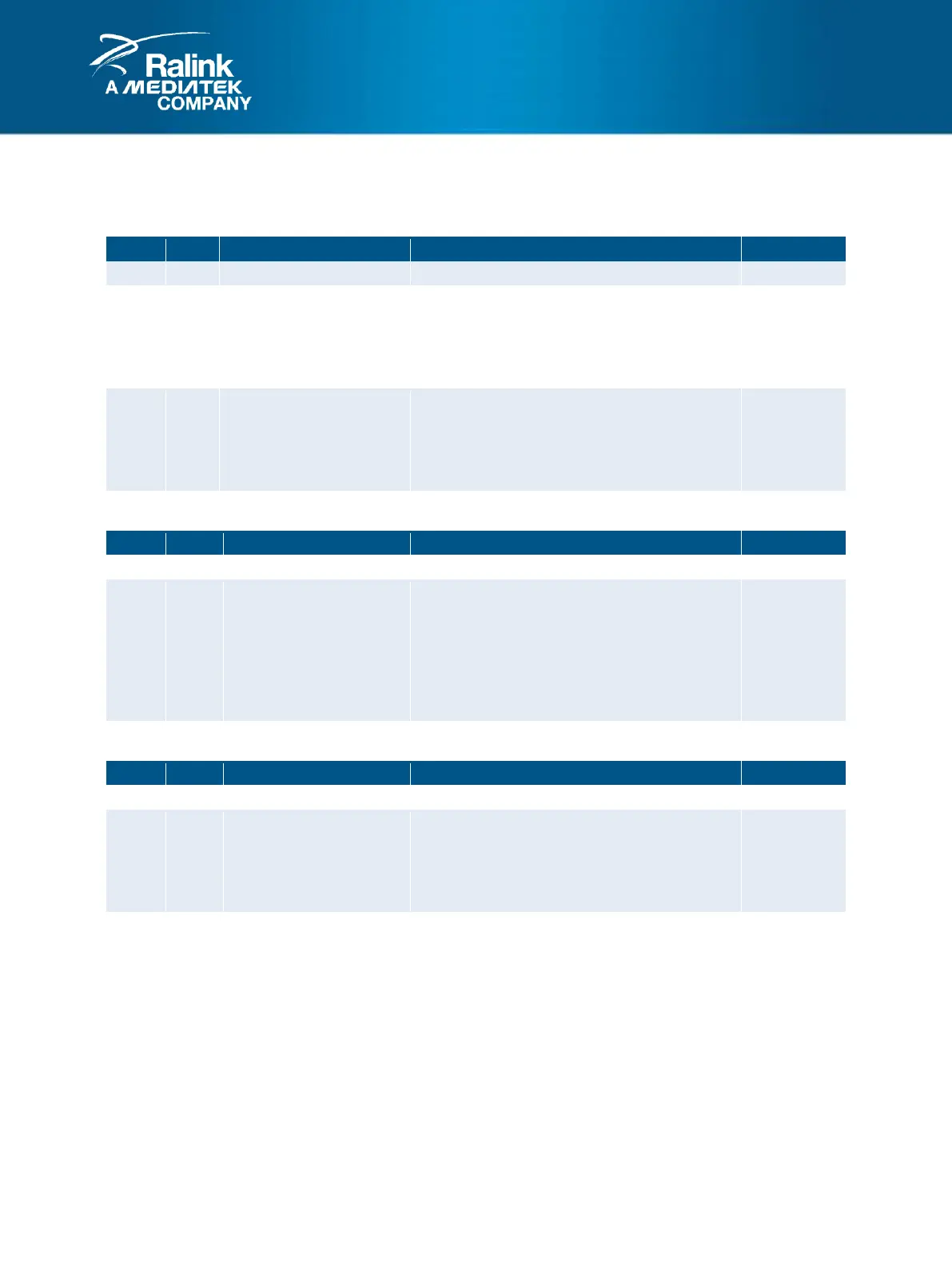

44. CMP_CNT: MIPS Compare Register (offset: 0x0004)

Compare Count

Sets the cutoff point for the free run counter

(MIPS counter). If the free run counter equals

the compare counter, then the timer circuit

generates an interrupt. The interrupt remains

active until the compare counter is written

again.

45. CNT: MIPS Counter Register (offset: 0x0008)

MIPS Counter

The MIPS counter (free run counter) increases

by 1 every 20 μs (50 KHz). The counter

continues to count until it reaches the value

loaded into CMP_CNT.

Loading...

Loading...