MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.13.4 Register Descriptions (base: 0x1000_0B00)

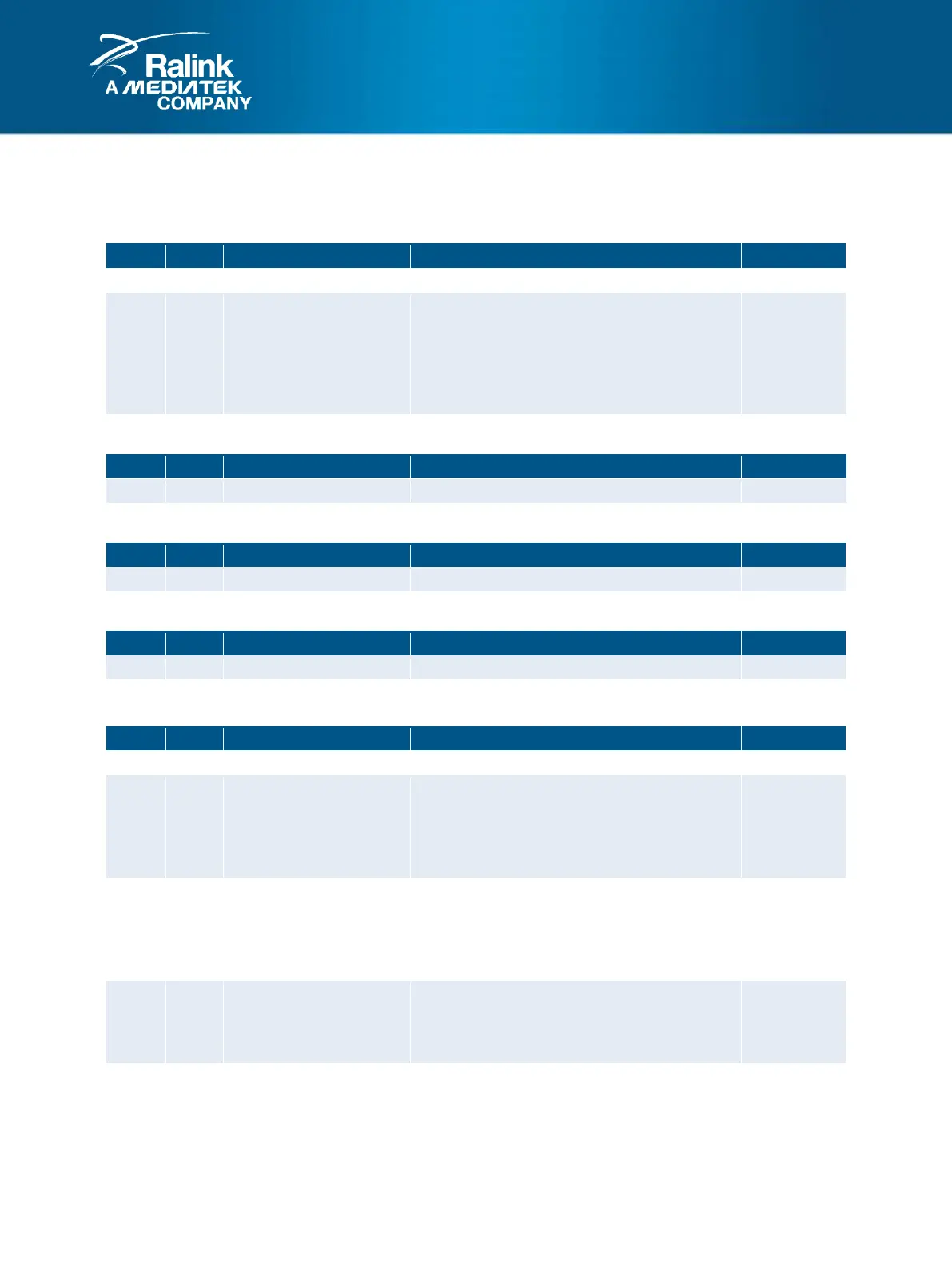

170. SPISTAT0: SPI Interface 0 Status (offset: 0x0000)

Indicates SPI transfer in progress

0: The SPI interface is inactive.

1: An SPI transfer is in progress.

NOTE: This bit must be set to 0 before initiating

a transfer. Any attempt to start a data transfer

is ignored if this bit is a 1.

171. Reserved (offset: 0x0004)

172. Reserved: (offset: 0x0008)

173. Reserved: (offset: 0x000C)

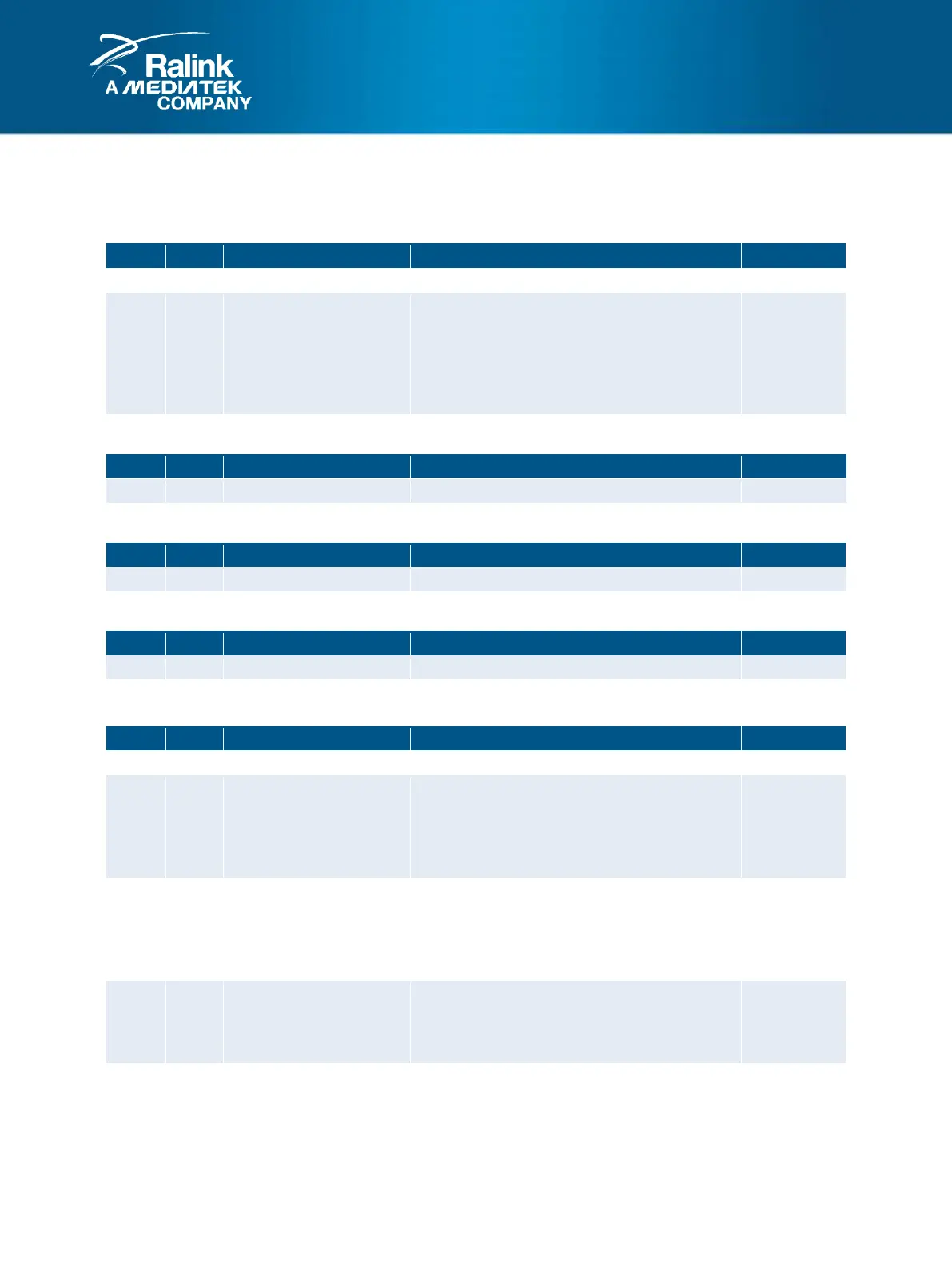

174. SPICFG0: SPI Interface 0 Configuration (offset: 0x0010)

SPI Address Mode

0: 3-Byte address mode

(for SPI flash <= 128 Mb)

1: 4-Byte address mode

(for SPI flash >= 256 Mb)

Rx Pre-Envelope Disable

Disables setting a pre-data input before the first

data is received.

0: Enable clock PRE_ENVELOP (slave mode)

1: Disable clock PRE_ENVELOP (SPI flash mode)

Rx Capture Delay Mode

0: Rx data capture is not delayed.

1: Rx data capture is delayed for half an SPICLK

cycle

Loading...

Loading...