MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

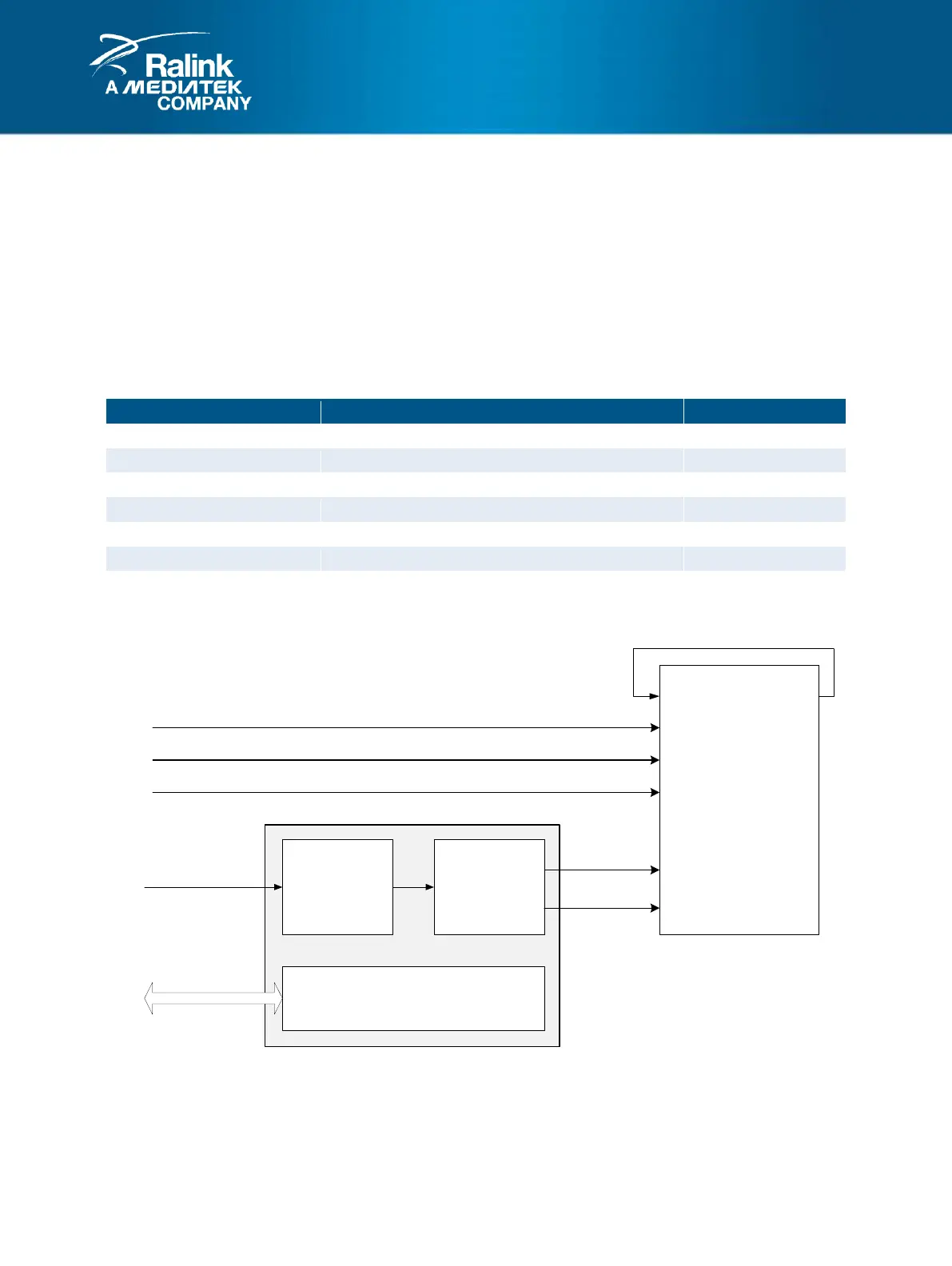

2.4 Interrupt Controller

2.4.1 Features

Supports a central point for interrupt aggregation for platform related blocks

Separated interrupt enable and disable registers

Supports global disable function

2-level Interrupt priority selection

Each interrupt source can be directed to IRQ#0 or IRQ#1

NOTE: MT7620 supports MIPS 24K’s vector interrupt mechanism.

There are 6 hardware interrupts supported by MIPS 24K. The interrupt allocation is shown below:

Other high priority interrupts (IRQ#1)

Other low priority interrupts (IRQ#0)

2.4.2 Block Diagram

Interrupt

Masking

Interrupt Priority

Selection

PalmBus Interface

Interrupts

(from platform blocks)

PalmBus

(to/from MIPS)

MIPS

Interrupt Controller

MIPS Timer INT

IRQ1

(high priority)

IRQ0

(low priority)

INT 5

INT 4

INT 3

INT 2

INT 1

INT 0

Figure 2-3 Interrupt Controller Block Diagram

Loading...

Loading...