MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

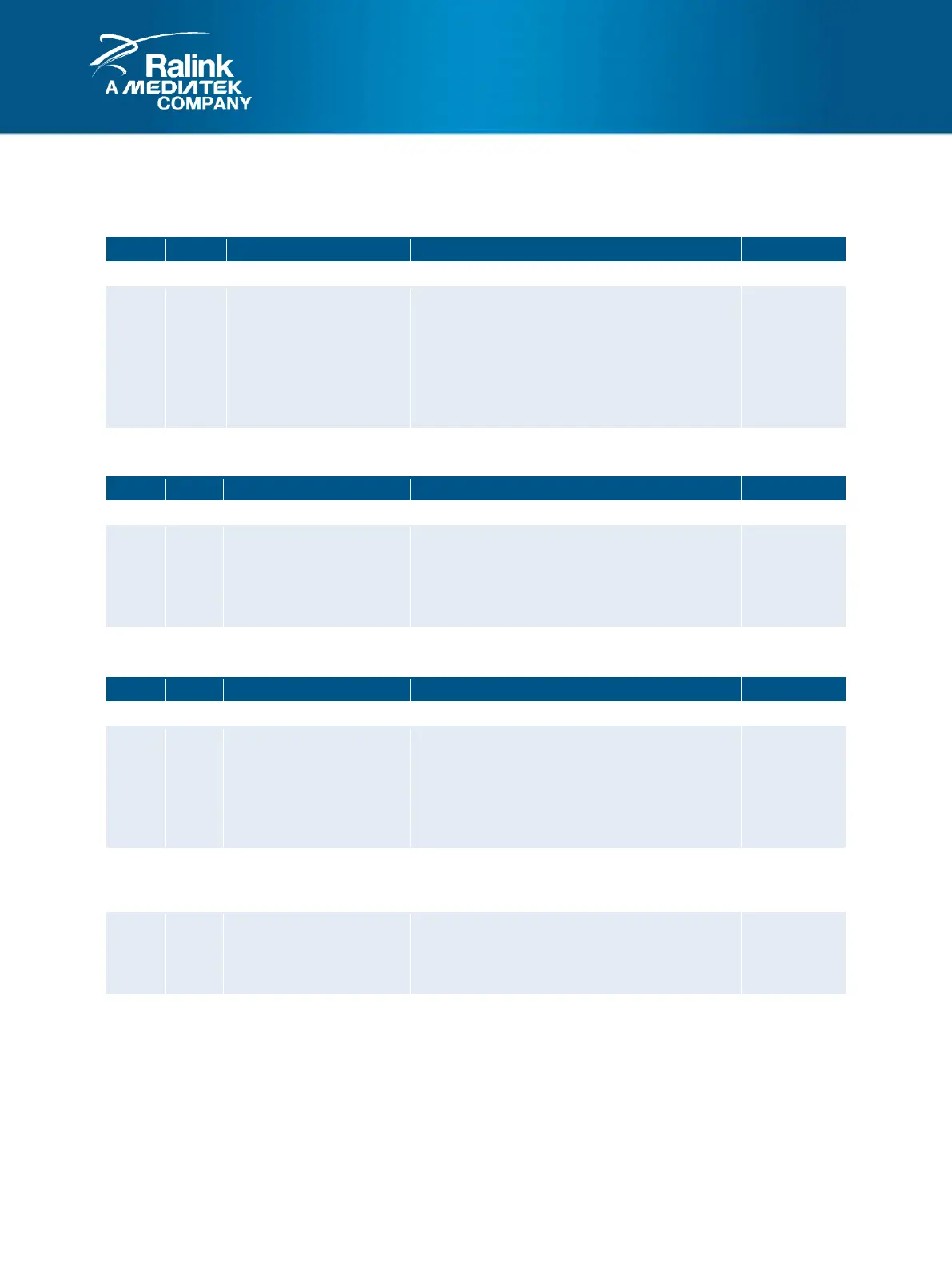

2.7.4 Register Descriptions (base: 0x1000_0C00)

59. RBR: Receive Buffer Register (offset: 0x0000)

Receive Buffer Data

Data is transferred to this register from the Rx

shift register after a full character is received.

The OE bit in the LSR register is set if the

contents of this register have not been read

before another character is received, indicating

an Rx buffer overrun.

60. TBR: Transmit Buffer Register (offset: 0x0004)

Transmit Buffer Data

When a character is written to this register, it is

stored in the Tx holding register; if the Tx

register is empty, the character is moved to the

Tx register, starting transmission.

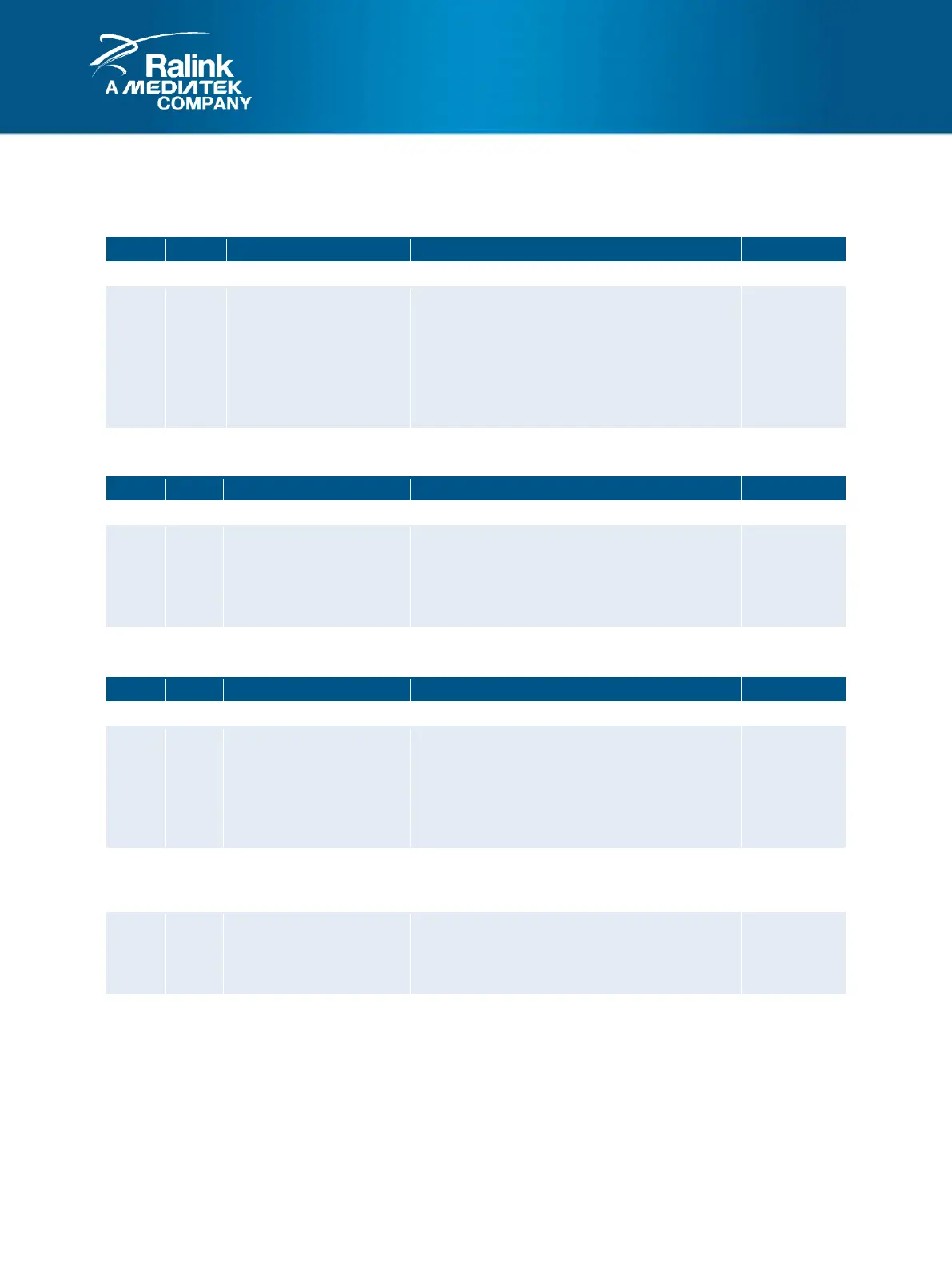

61. IER: Interrupt Enable Register (offset: 0x0008)

Enable Line Status Interrupts

Enables the following Rx line status interrupts.

Overrun Error (OE)

Parity Error (PE)

Framing Error (FE)

Break Interrupt (BI)

Enable Tx Buffer Empty Interrupt

Enables the Tx buffer empty interrupt (THRE),

which indicates the Tx buffer is empty.

Enable Rx Buffer Full Interrupt

Enables the Rx buffer full interrupt, as well as

the Data Ready (DR) and Character Time-Out

interrupts.

NOTE:

0: Disable

1: Enable

Loading...

Loading...