MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

2.3.4 Register Descriptions (base: 0x1000_0100)

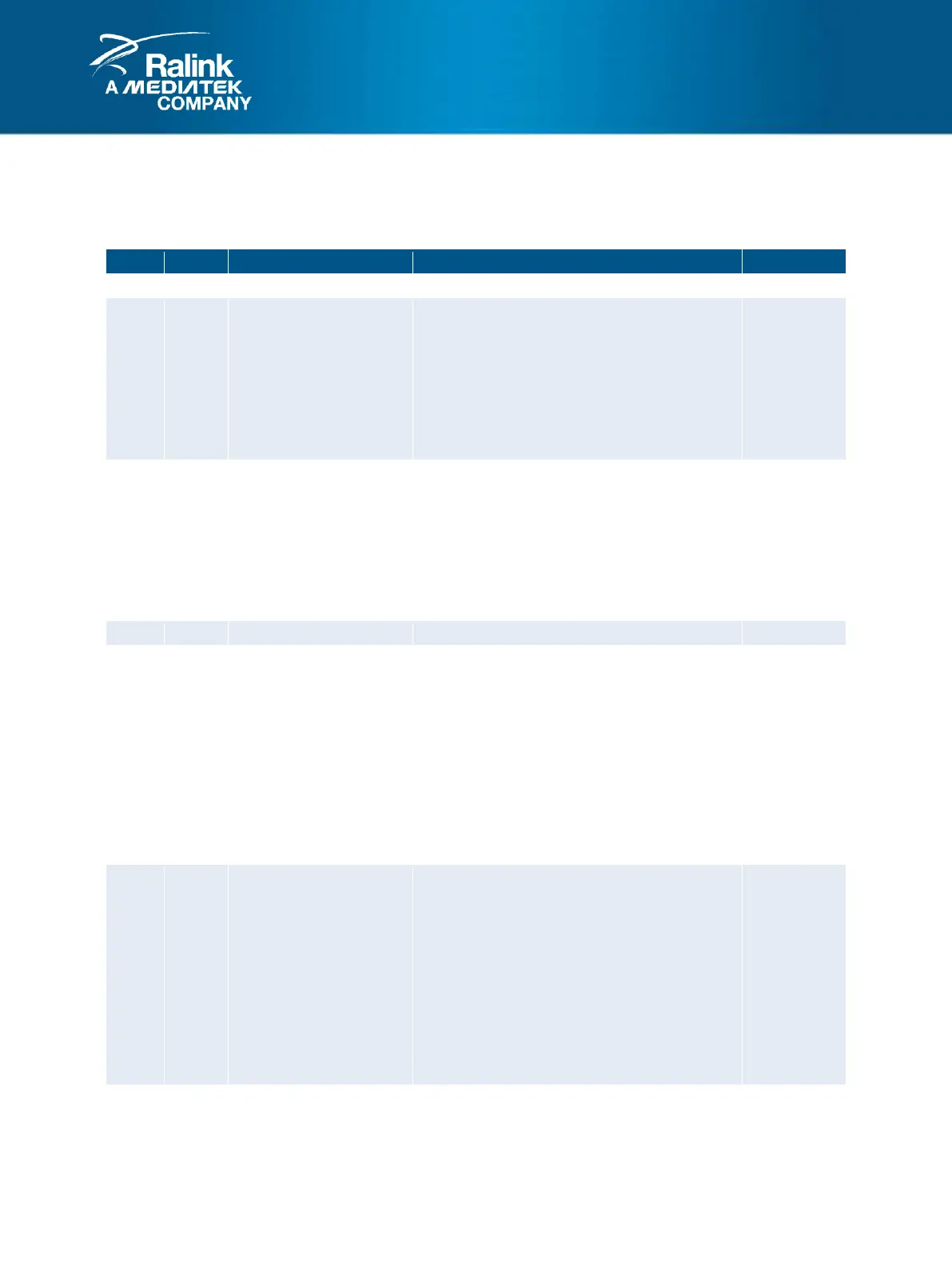

30. TMRSTAT: Timer Status Register (offset: 0x0000)

Timer 1 Reset

Read

Reading this bit returns a 0.

Write

0: No effect.

1: Reset Timer 1 to 0xFFFF if in free-running

mode, or to the value specified in the

TMR1LOAD register in all other modes.

Timer 0 Reset

Read

Reading this bit returns a 0.

Write

0: No effect.

1: Reset Timer 0 to 0xFFFF if in free-running

mode, or to the value specified in the

TMR0LOAD register in all other modes.

Timer 1 Interrupt Status

Indicates that timer 1 has expired and timer 1

interrupt to the processor has asserted. After

the interrupt is sent, the bit is written to 1 and

cleared.

Read

0: Not asserted.

1: Asserted.

Write

0: No effect

1: Clears the interrupt.

Timer 0 Interrupt Status

Indicates that timer 0 has expired and timer 0

interrupt to the processor has asserted. After

the interrupt is sent, the bit is written to 1 and

cleared.

Read

0: Not asserted.

1: Asserted.

Write

0: No effect

1: Clears the interrupt.

Loading...

Loading...