MT7620 PROGRAMMING GUIDE

Integrated 802.11n MAC/BBP and 2.4 GHz RF/FEM Router-on-a-Chip

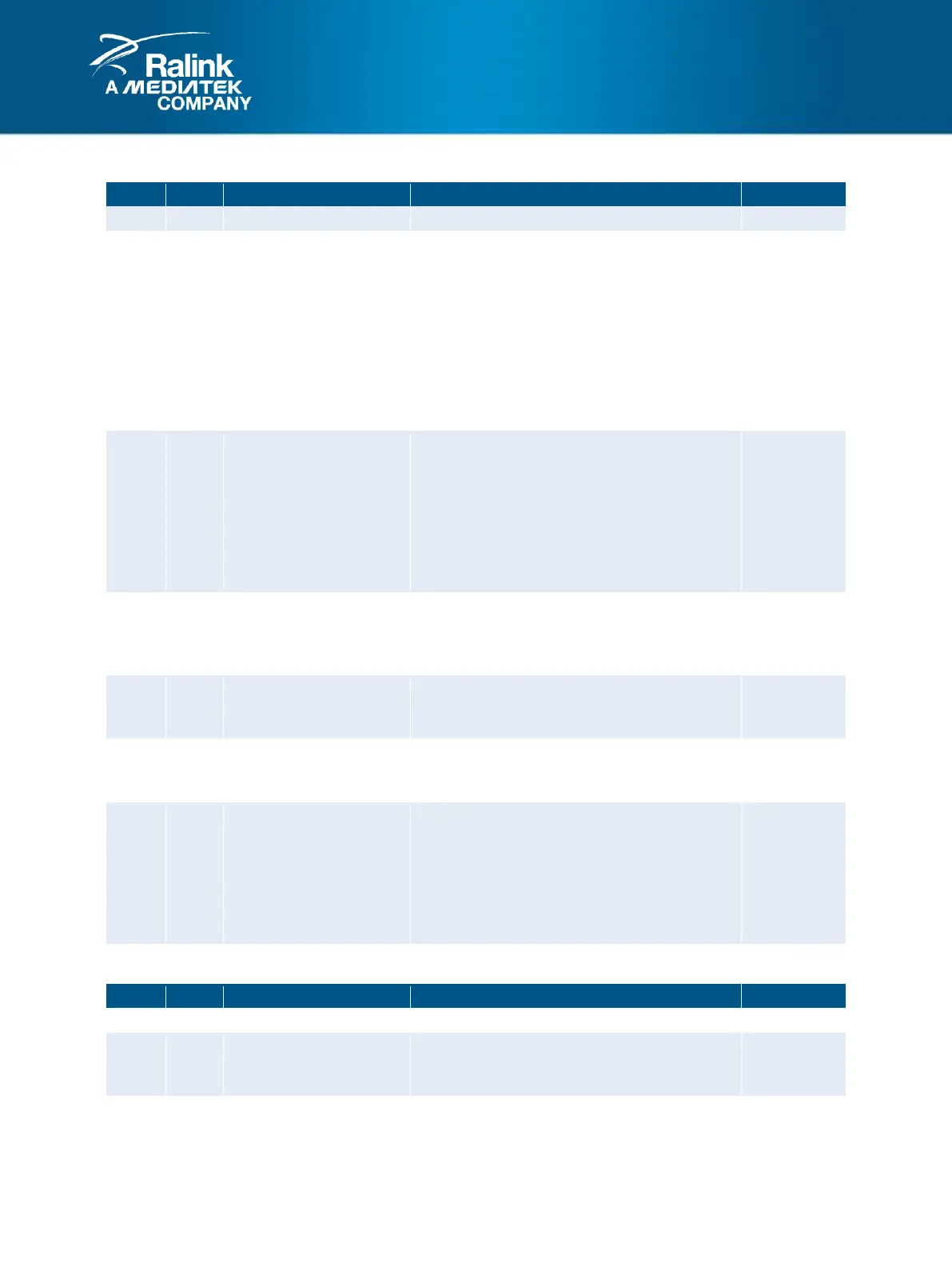

63. FCR: FIFO Control Register (offset: 0x0010)

Rx Trigger Level

Sets the number of characters contained by the

receive buffer which triggers the data ready

(DR) interrupt.

0: 1 character

1: 4 characters

2: 8 characters

3: 14 characters

NOTE: This register is not used if the Rx FIFO is

disabled.

Tx Trigger Level

Sets the number of characters contained by the

transmit buffer which will trigger the threshold

empty (THRE) interrupt.

0: 1 character

1: 4 characters

2: 8 characters

3: 12 characters

DMA Mode

Enables DMA transfers

This bit is writeable and readable, but has no

other hardware function.

Tx Reset

1: Clears the transmit FIFO and resets its status.

The shift register is not cleared.

Rx Reset

1: Clears the receive FIFO and resets its status.

The shift register is not cleared.

FIFO Enable

Enables Tx and Rx FIFOs. When disabled, the

FIFOs have an effective depth of one character.

0: Disable

1: Enable

NOTE: The FIFO status and data are

automatically cleared when this bit is changed.

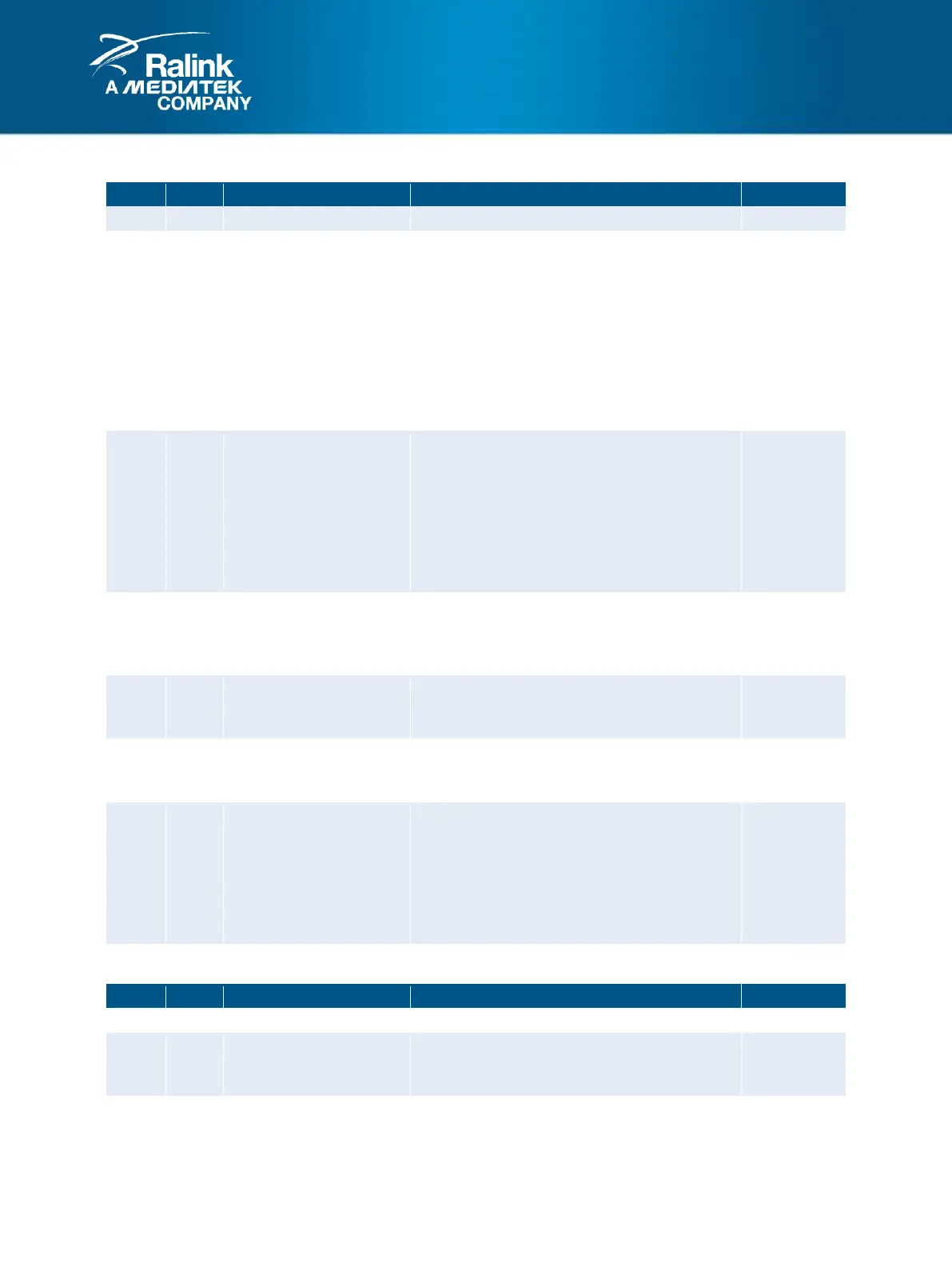

64. LCR: Line Control Register (offset: 0x0014)

Divisor Latch Access Bit

This bit has no functionality, and is retained for

compatibility only.

Loading...

Loading...