Timer A

M30240 Group

Rev.1.00 Sep 24, 2003 Page 160 of 360

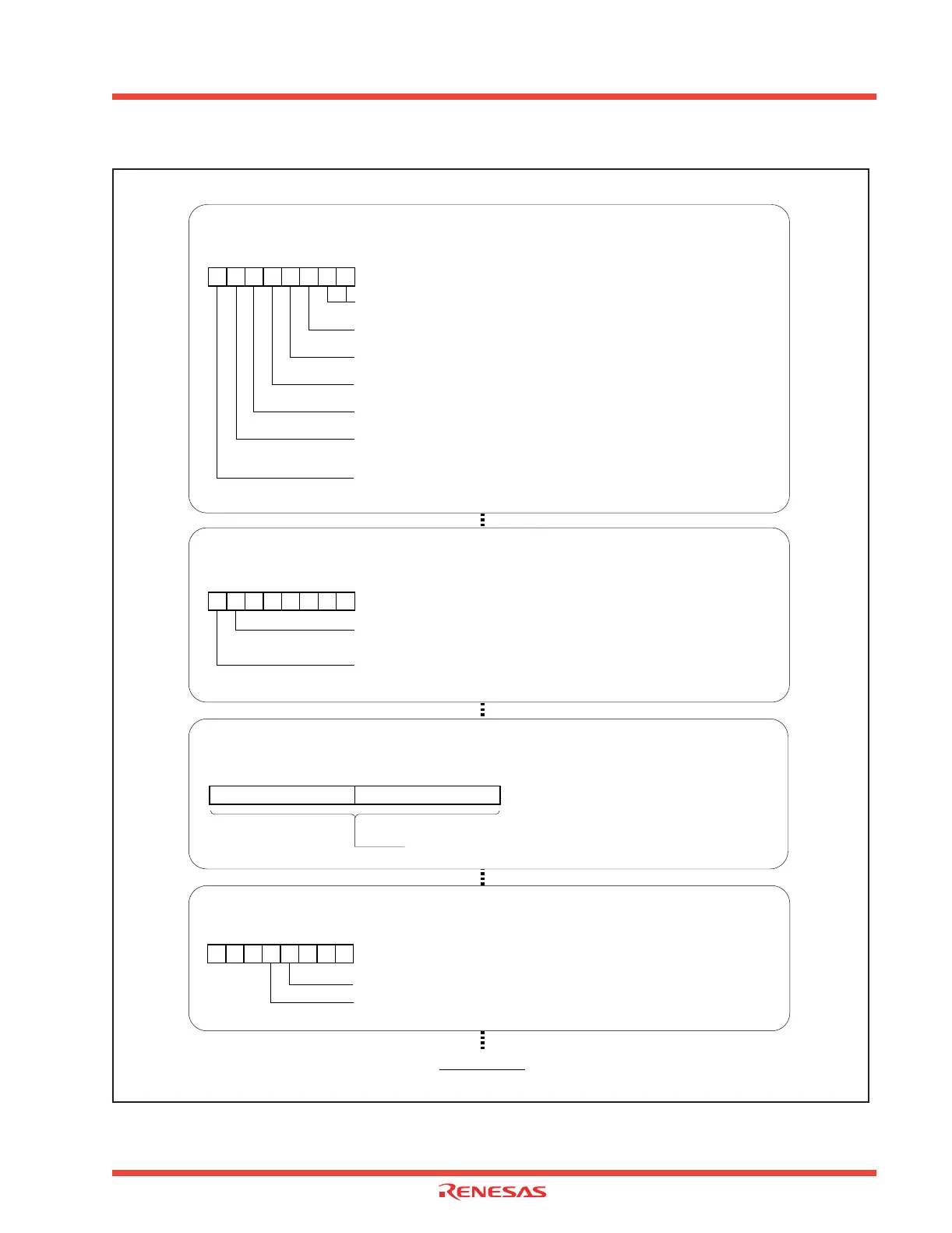

Figure 2.20: Set-up procedure of 2-phase pulse signal process in event counter mode, multiply by 4

Setting divide ratio

Can be set to 000016 to FFFF16

b7 b0

(b15) (b8)

b7 b0

Timer A3 register [Address 038D 16, 038C16] TA3

Timer A4 register [Address 038F

16, 038E16] TA4

Start count

Selecting event counter mode and functions

0 (Must always be “0” when using two-phase pulse signal processing)

Timer Ai mode register (i= 3, 4) [Address 0399 16, 039A16]

TAiMR (i= 3, 4)

1 (Must always be “1” when using two-phase pulse signal processing)

Selection of event counter mode

Two-phase pulse signal processing operation select bit

1 : Multiply-by-4 processing operation

Count operation type select bit

1 : Free-run type

0 (Must always be “0” when using two-phase pulse signal processing)

0 (Must always be “0” when using two-phase pulse signal processing)

b7 b0

01001011

Two-phase pulse signal processing select bit

b7 b0

Up/down flag [address 0384 16]

UDF

Timer A3 two-phase pulse signal processing select bit

1 : Two-phase pulse signal processing enabled

Timer A4 two-phase pulse signal processing select bit

1 : Two-phase pulse signal processing enabled

Setting count start flag

Count start flag [Address 0380 16]

TABSR

Timer A3 count start flag

Timer A4 count start flag

b7 b0

Loading...

Loading...