Programming Notes

M30240 Group

Rev.1.00 Sep 24, 2003 Page 137 of 360

1.5.5 Programming Notes

1.5.5.1 Accessing USB IN/OUT Control and Status Registers

Do not use read-modify-write instruction on these registers because they contain control and status

bits that can be changed by both hardware and software. There is a possibility that using a read-mod-

ify-write instruction might cause incorrect data to be written back to these registers. See Table 1.52

for a list of bits that may have incorrect data written to them and the value you should write back in

order to prevent this from occurring.

The Endpoint 1-4 IN CSR’s (EPiICS, i = 1-4) have a bit IN_PKT_RDY (bit 0) that is set to a “1” by the

firmware after a packet of data is loaded to the respective endpoint’s FIFO. This signifies that a packet

is ready for transmission. If the firmware wants to send a NULL packet to the host, it can simply write

a “1” to the IN_PKT_RDY bit without loading data to the FIFO. This bit is cleared by the hardware. If

the firmware manipulates (writes) the IN CSR for a purpose other than to signify to the hardware that

a data packet is ready for transmission (for instance, set/reset ISO bit, set/reset SEND_STALL bit), it

must make sure that a “0” is written back to the IN_PKT_RDY bit. Failure to do so could cause improp-

er operation of the device. Writing a “0” to the IN_PKT_RDY bit has no effect on its state.

The Endpoint 1-4 OUT CSRs (EPiICS, i = 1-4) have a bit OUT_PKT_RDY (bit 0) that is set to a “1” by

the hardware after a packet of data is received from the host to the respective endpoint’s FIFO. This

signifies that a packet is ready for download. This bit is cleared by the firmware by writing a “0” to it

after the data packet is unloaded from the FIFO. If the firmware manipulates (writes) the OUT CSR for

a purpose other than to signify to the hardware that a data packet has been unloaded (for instance,

set/reset ISO bit, set/reset SEND_STALL bit), it must make sure that a “1” is written back to the

OUT_PKT_RDY bit. Failure to do so could cause improper operation. Writing a “1” to the

OUT_PKT_RDY bit has no effect on its state.

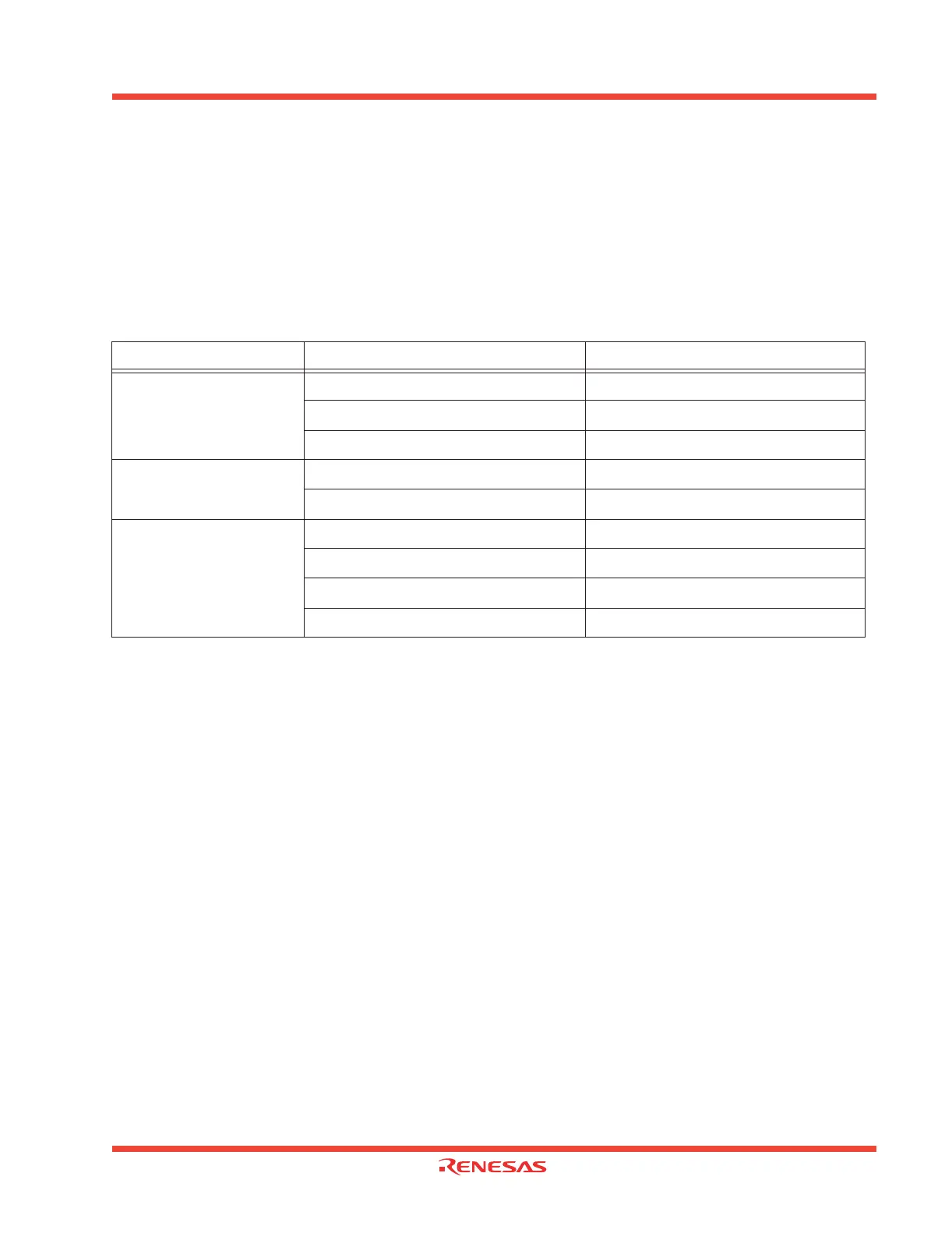

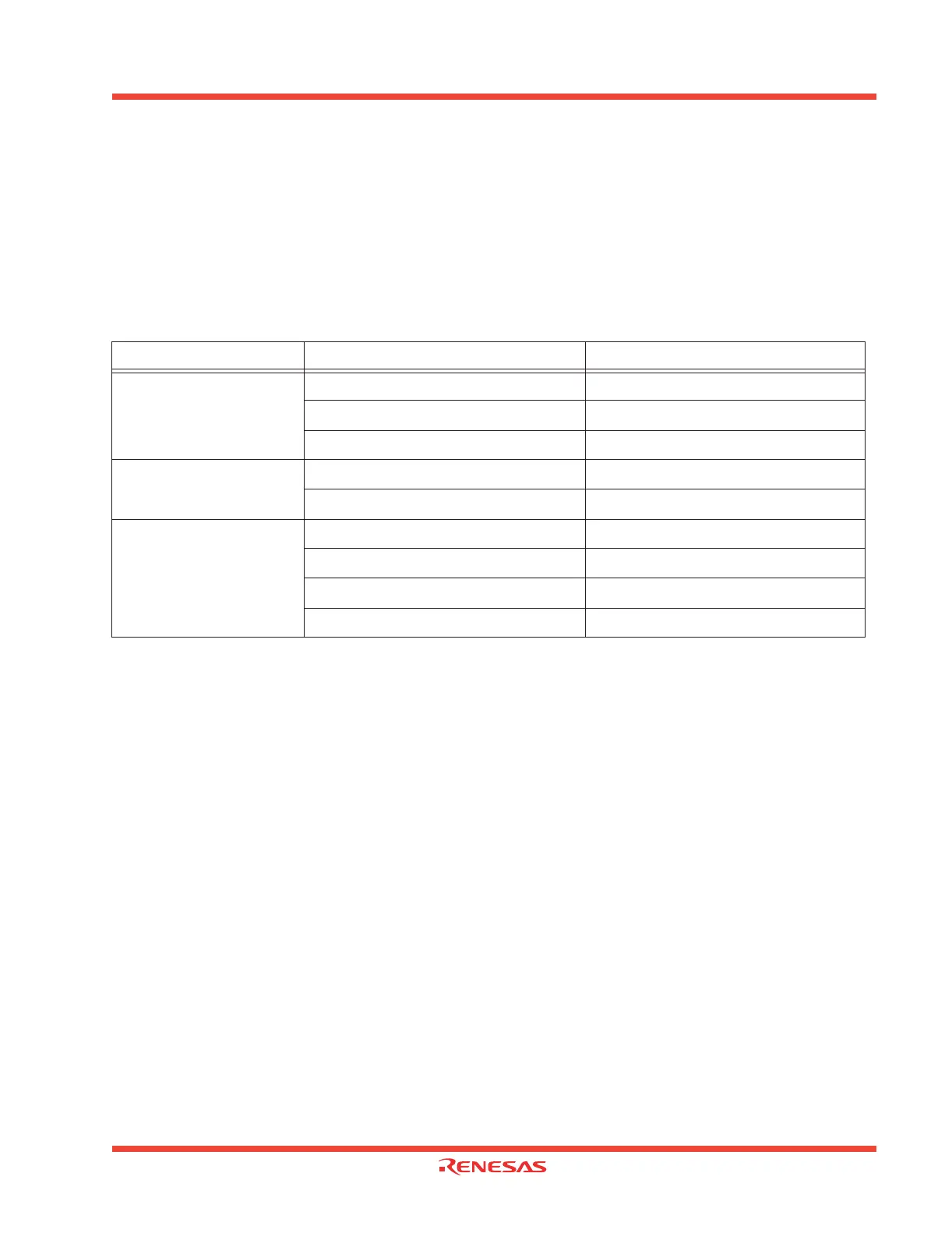

Table 1.52: Bits that might have incorrect data

Register name Bit name Value to write for “No change”

EP0CS

IN_PKT_RDY (b1) “0”

DATA_END (b3) “0”

FORCE_STALL (b4) “1”

EPxICS (x = 1-4)

IN_PKT_RDY (b0) “0”

UNDER_RUN (b1) “1”

EPxOCS (x = 1-4)

OUT_PKT_RDY (b0) “1”

OVER_RUN (b1) “1”

FORCE_STALL (b4) “1”

DATA-ERR (b5) “1”

Loading...

Loading...