Overview of Interrupts

M30240 Group

Rev.1.00 Sep 24, 2003 Page 338 of 360

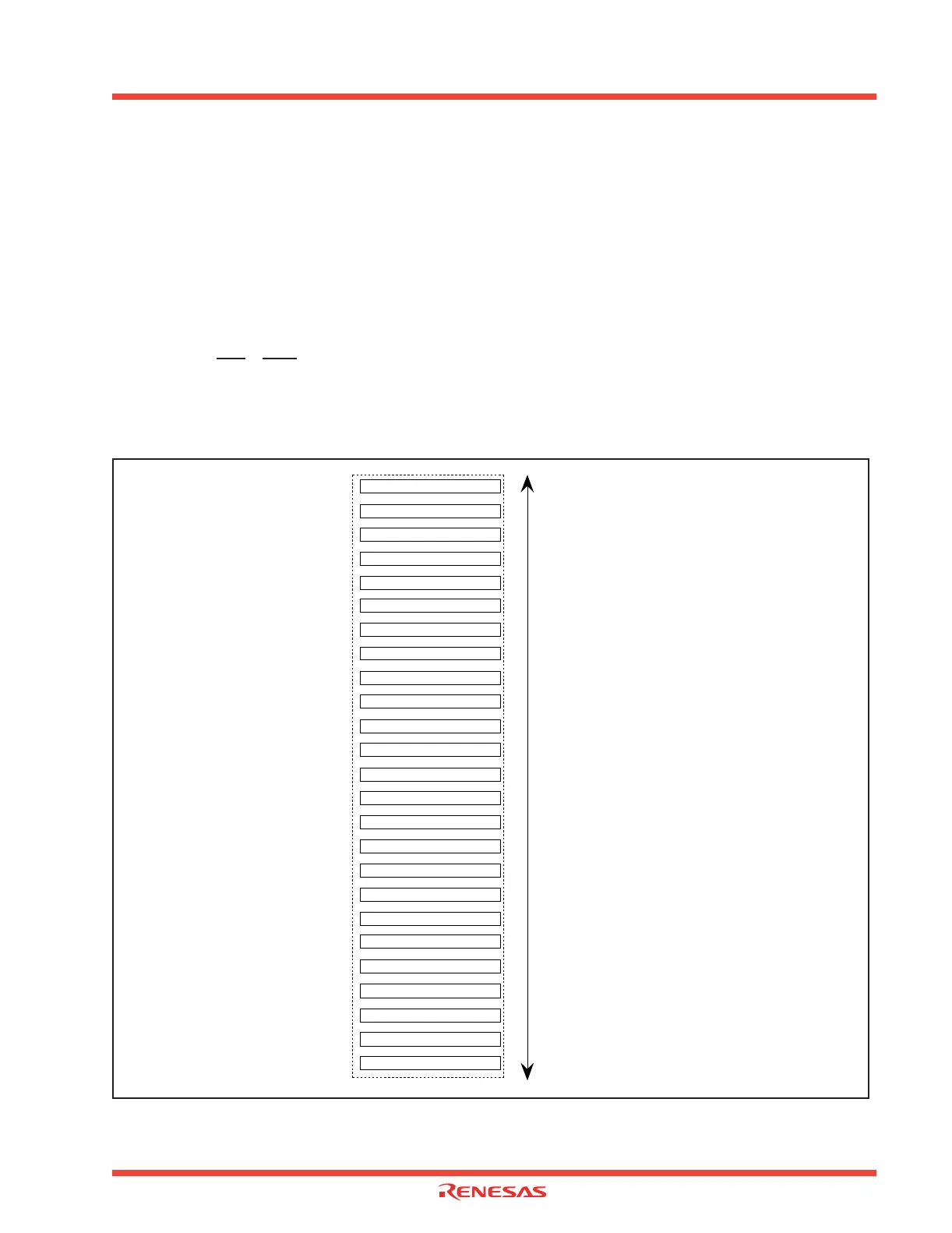

4.1.3.4 Interrupt Priority

If there are two or more interrupt requests occurring at a point in time within a single sampling (check-

ing whether interrupt requests are made), the interrupt assigned a higher priority is accepted.

Assign an arbitrary priority to maskable interrupts (peripheral I/O interrupts) using the interrupt priority

level select bit. If the same interrupt priority level is assigned, the interrupt assigned a higher hardware

priority is accepted (see Figure 4.4).

Priorities of the special interrupts, such as Reset (dealt with as an interrupt assigned the highest pri-

ority), watchdog timer interrupt, etc. are regulated by hardware.

The following indicates priorities of the hardware interrupts:

Reset > NMI > DBC > Watchdog timer > Peripheral I/O > Single step > Address match

Software interrupts are not affected by the interrupt priority. If an instruction is executed, control

branches invariably to the interrupt routine.

Figure 4.4: Maskable interrupts priorities (peripheral I/O interrupts)

USB Reset

Timer A4

Timer A2

USB SOF

UART1 reception

UART0 reception

UART2 reception

A-D conversion

DMA1

Bus collision detection

Timer A0

UART1 transmission

UART0 transmission

UART2 transmission

Key input interrupt

DMA0

INT1

Timer B1

Priority of peripheral I/O interrupts

(if priority levels are same)

USB Suspend

USB Resume

USB Function

Timer A3

Timer A1

INT0

Timer B0

High

Low

Loading...

Loading...