Clock-Asynchronous Serial I/O

M30240 Group

Rev.1.00 Sep 24, 2003 Page 217 of 360

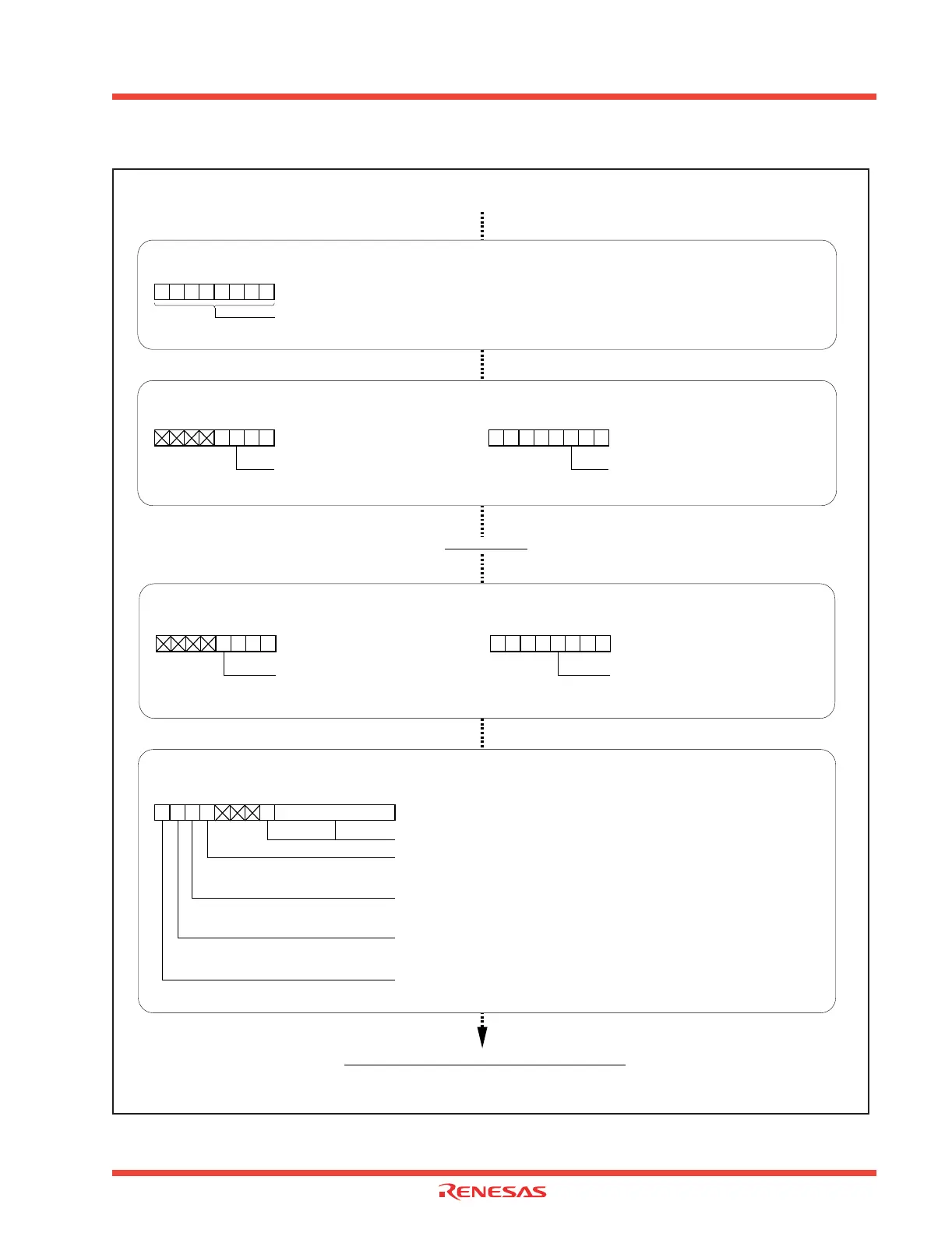

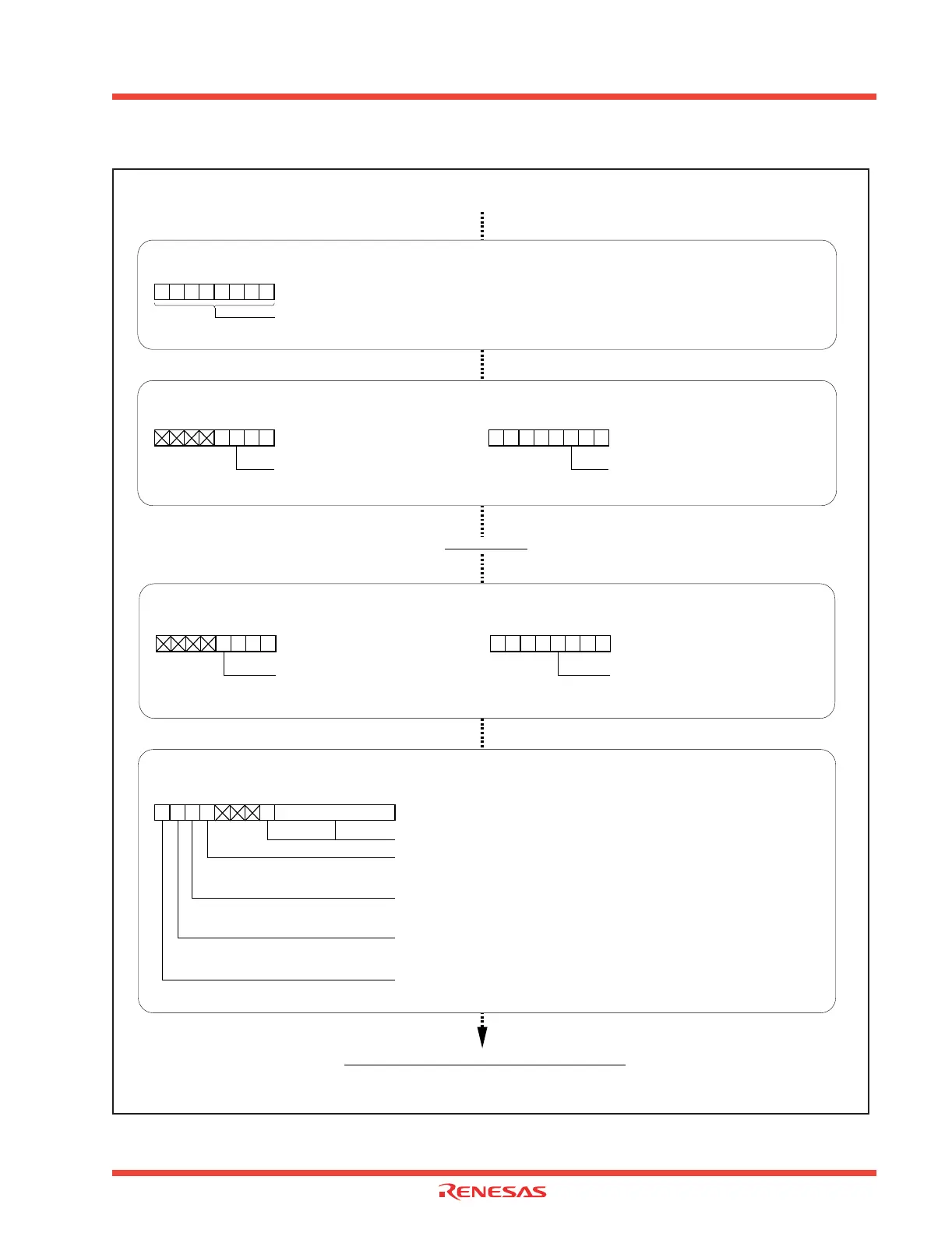

Figure 2.67: Set-up procedure of reception in UART mode (2)

Start reception

Processing after reading out reception data

Continued from the previous page

Checking error

UART0 receive buffer register [Address 03A7

16

, 03A6

16

]U0RB

UART1 receive buffer register [Address 03AF

16

, 03AE

16

]U1RB

UART2 receive buffer register [Address 037F

16

, 037E

16

]U2RB

Overrun error flag

0 : No overrun error

1 : Overrun error found

b7 b0 b7 b0

(b15) (b8)

Receive data

Framing error flag

0 : No framing error

1 : Framing error found

Parity error flag

0 : No parity error

1 : Parity error found

Error sum flag

0 : No error

1 : Error found

Setting UARTi bit rate generator(i = 0 to 2)

UARTi bit rate generator (i = 0 to 2) [Address 03A1

16

, 03A9

16

, 0379

16

]

UiBRG (i = 0 to 2)

Can be set from 00

16

to FF

16

(Note)

b7 b0

Note: Write to UARTi bit rate generator when transmission/reception is halted.

Reception enabled

UART0 transmit/receive control register 1

U0C1 [Address 03A5

16

]

UART1 transmit/receive control register 1

U1C1 [Address 03AD

16

]

b7 b0

Receive enable bit

1 : Reception enabled

1

UART2 transmit/receive control register 1

U2C1 [Address 037D

16

]

b7 b0

Receive enable bit

1 : Reception enabled

1

Checking completion of reception

UART0 transmit/receive control register 1

U0C1 [Address 03A5

16

]

UART1 transmit/receive control register 1

U1C1 [Address 03AD

16

]

b7 b0

Receive complete flag

0 : No data present in receive buffer register

1 : Data present in receive buffer register

UART2 transmit/receive control register 1

U2C1 [Address 037D

16

]

b7 b0

Receive complete flag

0 : No data present in receive buffer register

1 : Data present in receive buffer register

Loading...

Loading...