A-D Converter

M30240 Group

Rev.1.00 Sep 24, 2003 Page 240 of 360

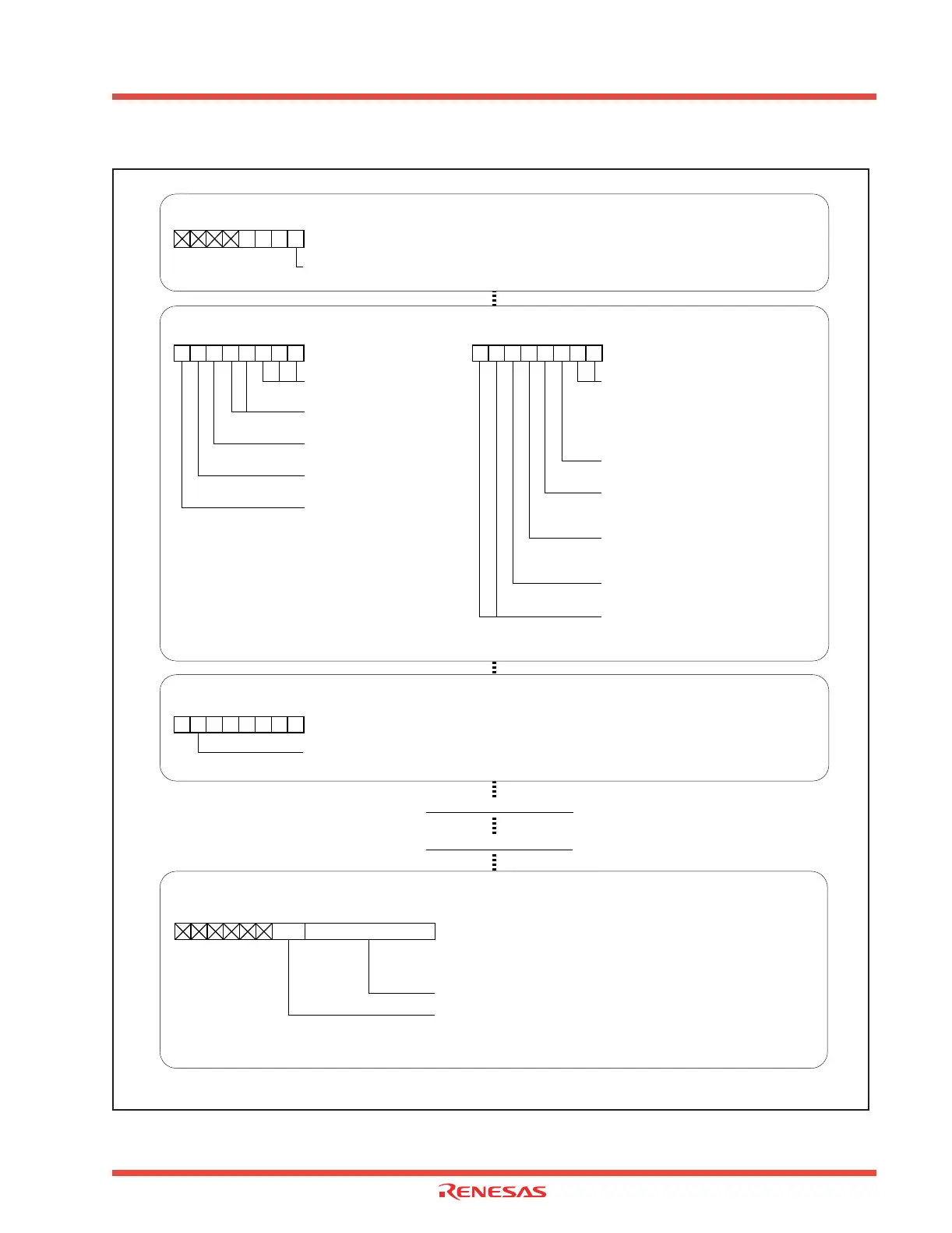

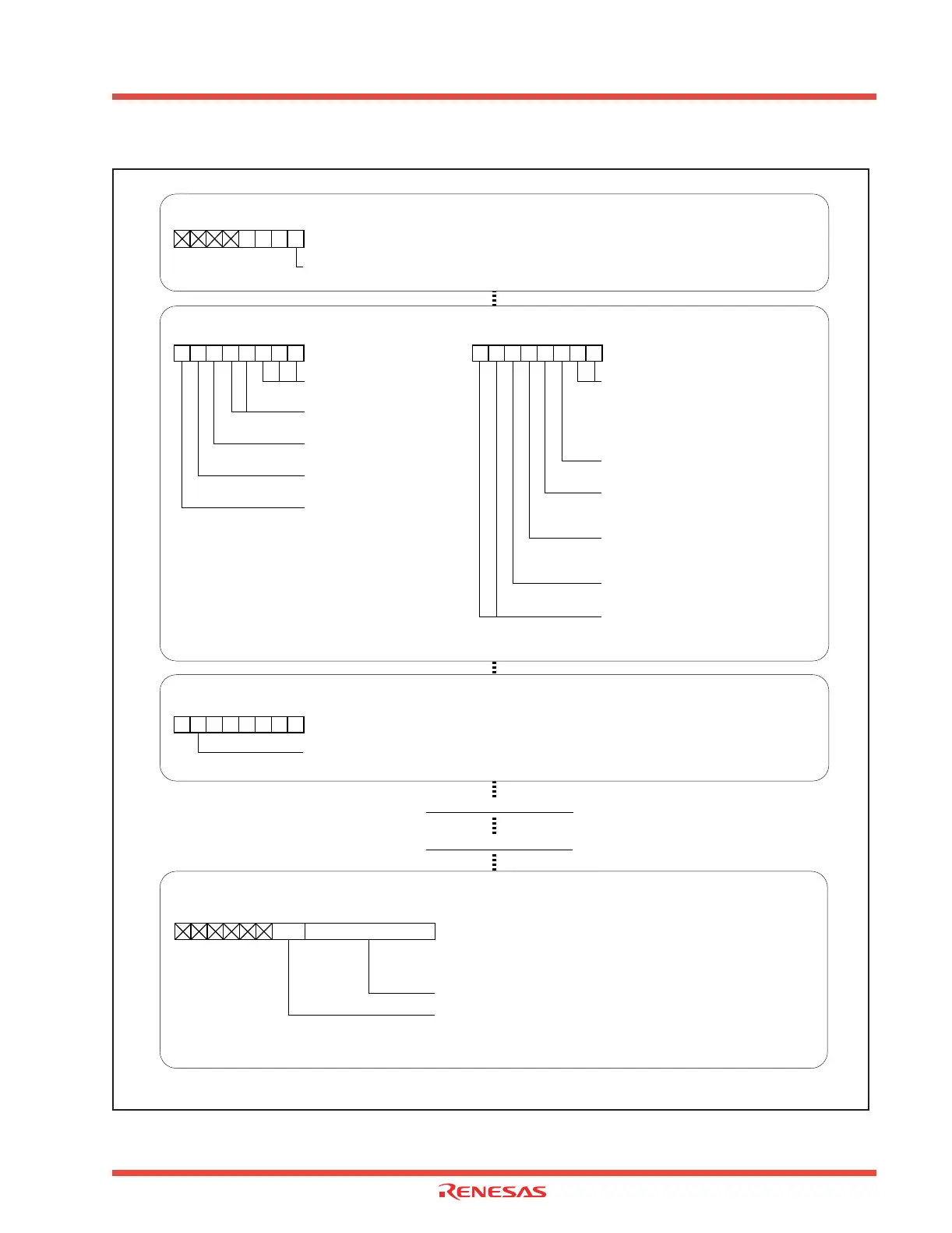

Figure 2.86: Set-up procedure of single-sweep mode

b7 b0

1

Setting A-D conversion start flag

A-D control register 0 [Address 03D6 16]

ADCON0

A-D conversion start flag

1 : A-D conversion started

Reading conversion result

Eight low-order bits of A-D conversion result

b7 b0

(b15) (b8)

b7 b0

A-D register 0 [Address 03C116, 03C016] AD0

A-D register 1 [Address 03C3

16, 03C216] AD1

A-D register 2 [Address 03C5

16, 03C416] AD2

A-D register 3 [Address 03C7

16, 03C616] AD3

A-D register 4 [Address 03C9

16, 03C816] AD4

A-D register 5 [Address 03CB

16, 03CA16] AD5

A-D register 6 [Address 03CD

16, 03CC16] AD6

A-D register 7 [Address 03CF

16, 03CE16] AD7

During 10-bit mode

Two high-order bits of A-D conversion result

During 8-bit mode

When read, the content is indeterminate

Start A-D conversion

Stop A-D conversion

b7 b0

Setting A-D control register 0 and A-D control register 1

A-D control register 0

[Address 03D6

16] ADCON0

A-D sweep pin select bit (Note)

0 0 : AN

0, AN1 (2 pins)

0 1 : AN

0 to AN3 (4 pins)

1 0 : AN

0 to AN5 (6 pins)

1 1 : AN

0 to AN7 (8 pins)

b1 b0

b7 b0

A-D control register 1 [Address 03D7 16]

ADCON1

A-D operation mode select bit 1 (Note)

0 (Must always be “0” in Single sweep mode)

8/10-bit mode select bit

0 : 8-bit mode

1 : 10-bit mode

Frequency select bit 1

0 : f

AD/2 or fAD/4 is selected

1 : f

AD is selected

Single sweep mode is selected

(Note)

Trigger select bit

0 : Software trigger

A-D conversion start flag

0 : A-D conversion disabled

Frequency select bit 0

0 : f

AD/4 is selected

1 : f

AD/2 is selected

0010

Vref connect bit

1 : Vref connected

Reserved bits. Always set to "0"

00 01

Invalid in single sweep mode

b7 b0

Selecting Sample and hold

A-D control register 2 [Address 03D4 16]

ADCON2

A-D conversion method select bit

1 : With sample and hold

1

Note: Rewrite the analog input pin select bit after changing A-D operation mode.

0

0

0

Loading...

Loading...