A-D Converter

M30240 Group

Rev.1.00 Sep 24, 2003 Page 249 of 360

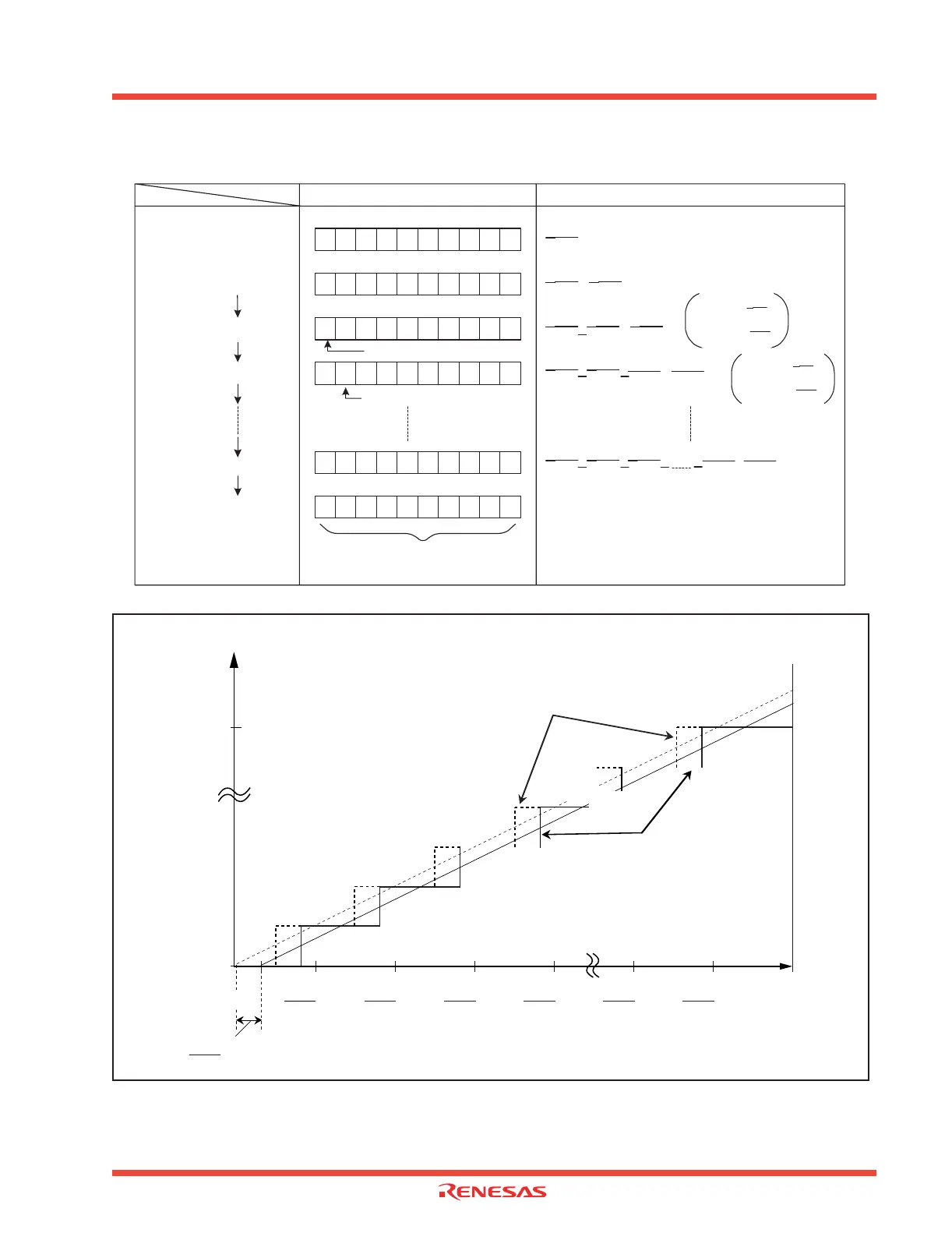

Table 2.36: Variation of successive comparison register and Vref while A-D converter is in progress

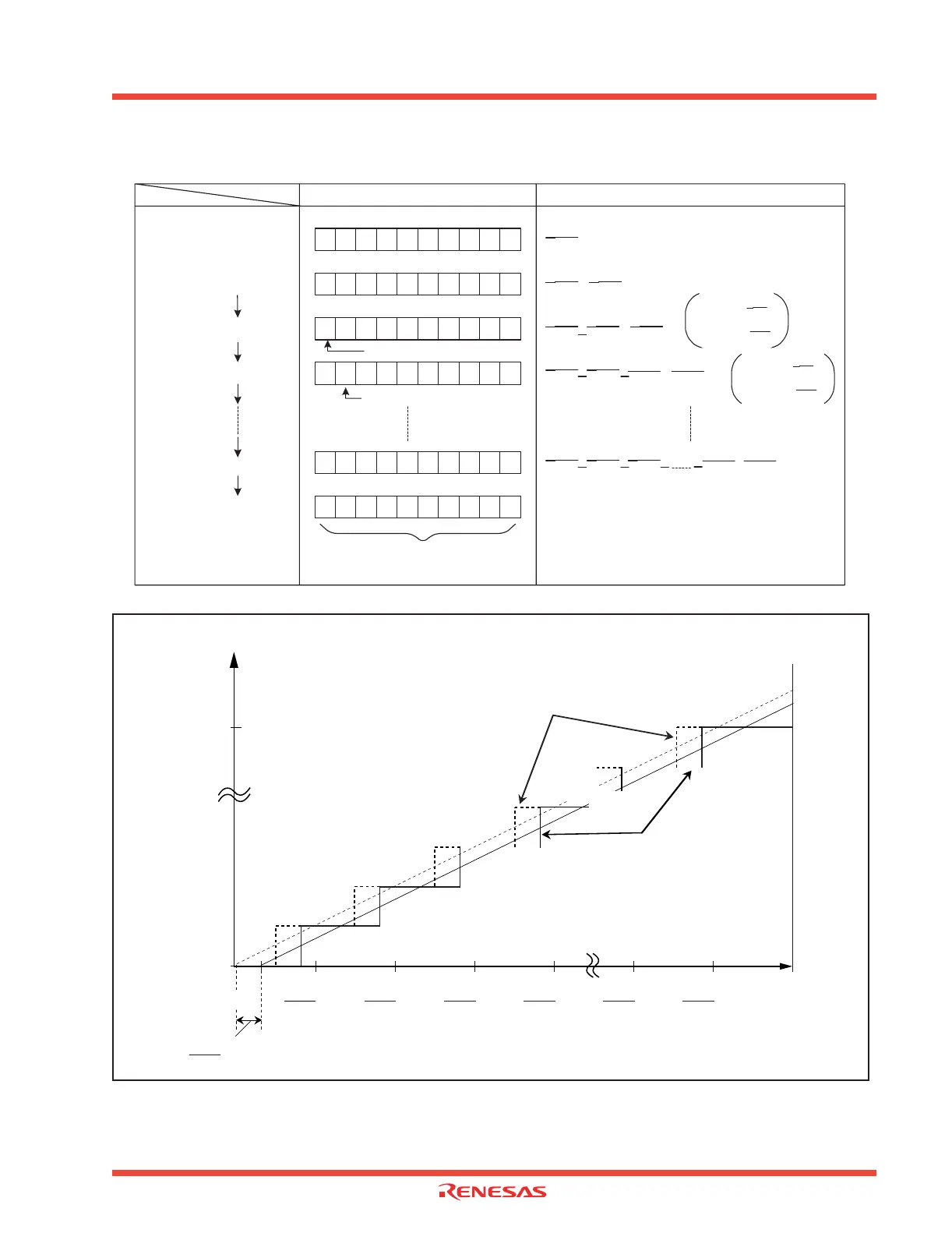

Figure 2.95: Theoretical A-D conversion characteristics (8-bit mode)

b9 b0

1 0 0 0 0 0 0 0 0 0

1 0 0 0 0 0 0 0 0 0

n9

1 0 0 0 0 0 0 0 0

n9 n8

1 0 0 0 0 0 0 0

n9 n8 n7 n6 n5 n4 n3 1 0 0

n9 n8 n7 n6 n5 n4 n3 n2 0 0

VREF

2

VREF

2

VREF

2

VREF

2

VREF

2

[V]

VREF

2048

[V]

VREF

2048

VREF

4

[V]

VREF

4

VREF

8

VREF

2048

VREF

4

VREF

8

VREF

256

VREF

2048

[V]

[V]

n9=1 + VREF

4

n9=0 - V

REF

4

n8=1 + VREF

8

n8=0 - V

REF

8

A-D converter stopped

1st comparison

2nd comparison

3rd comparison

8th comparison

Conversion complete

1st comparison result

2nd comparison result

This data transfers to bit 0 and

bit 7 of A-D register

+

+ +

+ + +

+

-

-

-

-

Successive approximation register VREF change

0016

0116

0216

0316

FE16

FF16

Result of A-D conversion

Analog input voltage

x 2

V

REF

256

VREF

256

x 3

x 4

V

REF

256

VREF

256

x 254

VREF

256

x 255

VREF

VREF

2048

x 3

Theoretical A-D conversion

characteristic of general 8-bit

A-D converter

0

VREF

256

x 1

Theoretical A-D conversion

characteristic in the 8-bit mode

Loading...

Loading...