DMAC

M30240 Group

Rev.1.00 Sep 24, 2003 Page 262 of 360

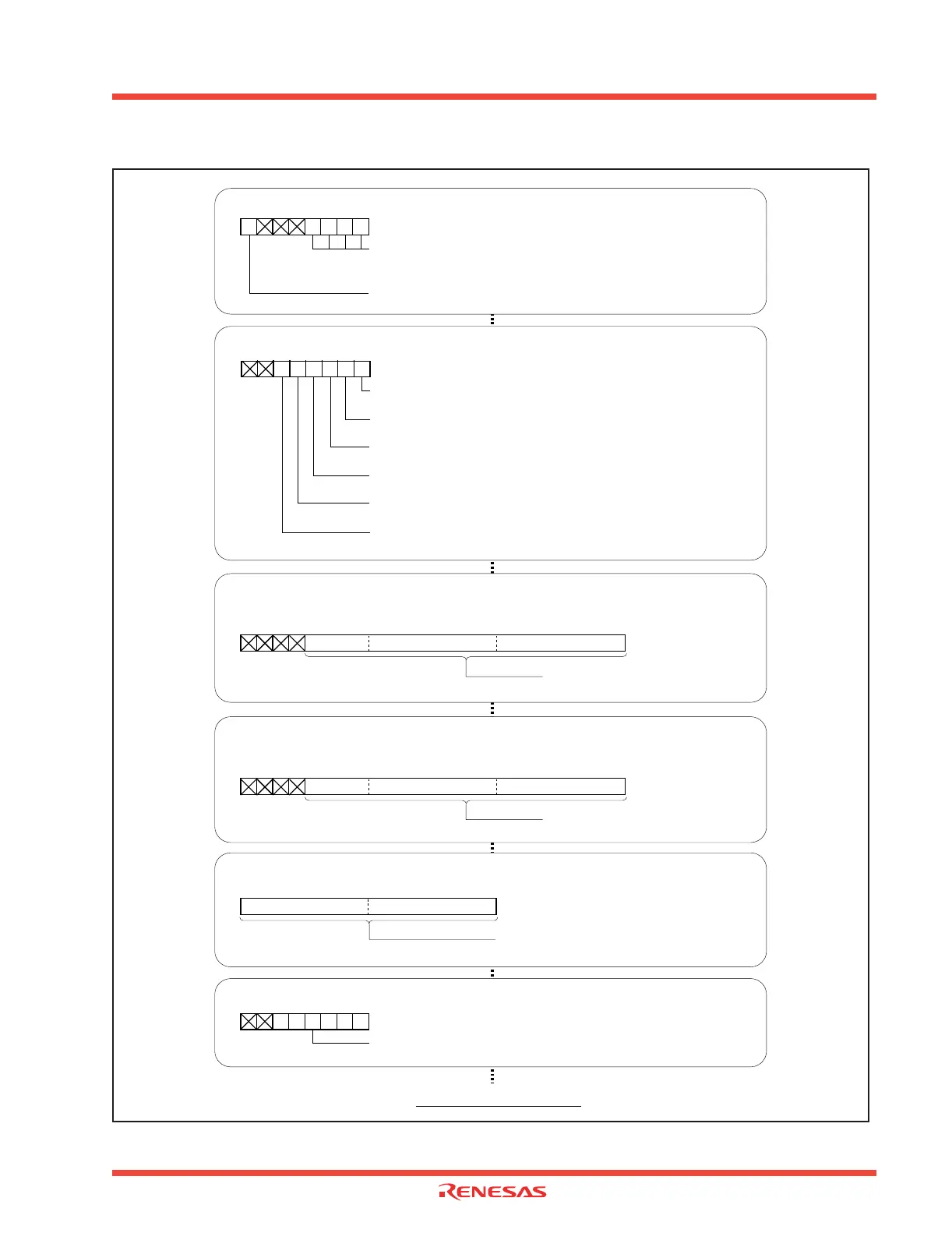

Figure 2.106: Set-up procedure for repeat transfer mode

When software DMA request bit = “1”

Setting DMAi request cause select register

DMAi request cause select register (i = 0, 1) [Address 03B8 16, 03BA16]

DMiSL(i = 0, 1)

b7 b0

01000

Software DMA request bit

Set to “0”

Setting DMAi control register

DMAi control register (i = 0, 1) [Address 002C 16, 003C16]

DMiCON(i = 0, 1)

Transfer unit bit select bit

0 : 16 bits

Repeat transfer mode select bit

1 : Repeat transfer

DMA request bit

0 : DMA not requested

DMA enable bit

0 : Disabled

Source address direction select bit

0 : Fixed (Bit 4 and bit 5 cannot be set to “1” simultaneously)

Destination address direction select bit

1 : Forward (Bit 4 and bit 5 cannot be set to “1” simultaneously)

b7 b0

100010

Setting DMAi source pointer

Source pointer

Stores the source address

b7 b0

(b15) (b8)

b7 b0b7 b0

(b16)(b23)

DMA0 source pointer [Address 0022 16 to 002016] SAR0

DMA1 source pointer [Address 0032

16 to 003016] SAR1

b3

(b19)

Setting DMAi destination pointer

Destination pointer

Stores the destination address

b7 b0

(b15) (b8)

b7 b0b7 b0

(b16)(b23)

DMA0 destination pointer [Address 0026 16 to 002416] DAR0

DMA1 destination pointer [Address 0036

16 to 003416] DAR1

b3

(b19)

Setting DMAi transfer counter

Transfer counter

Set a value one less than the transfer count

b0

b7 b0

DMA0 transfer counter [Address 0029 16, 002816] TCR0

DMA1 transfer counter [Address 0039

16, 003816] TCR1

b0

(b15)

Setting DMAi control register

DMAi control register (i = 0, 1) [Address 002C 16, 003C16]

DMiCON(i = 0, 1)

DMA enable bit

1 : Enabled

b7 b0

1

Note: Clear DMA request bit simultaneously again.

DMA request cause select bit

0 0 0 1 : Software trigger

b3 b2 b1 b0

Start DMA transmission

(b8)

Loading...

Loading...