Central Processing Unit

M30240 Group

Rev.1.00 Sep 24, 2003 Page 12 of 360

1.2.1.8.9 Bits 8 to 11: Reserved area

1.2.1.8.10 Bits 12 to 14: Processor interrupt priority level (IPL)

Processor interrupt priority level (IPL) is configured with three bits, for specification of up to eight processor

interrupt priority levels from level 0 to level 7.

If a requested interrupt has priority greater than the processor interrupt priority level (IPL), the interrupt is en-

abled.

1.2.1.8.11 Bit 15: Reserved area

The C, Z, S, and O flags are changed when instructions are executed. See the M16C software manual

for details.

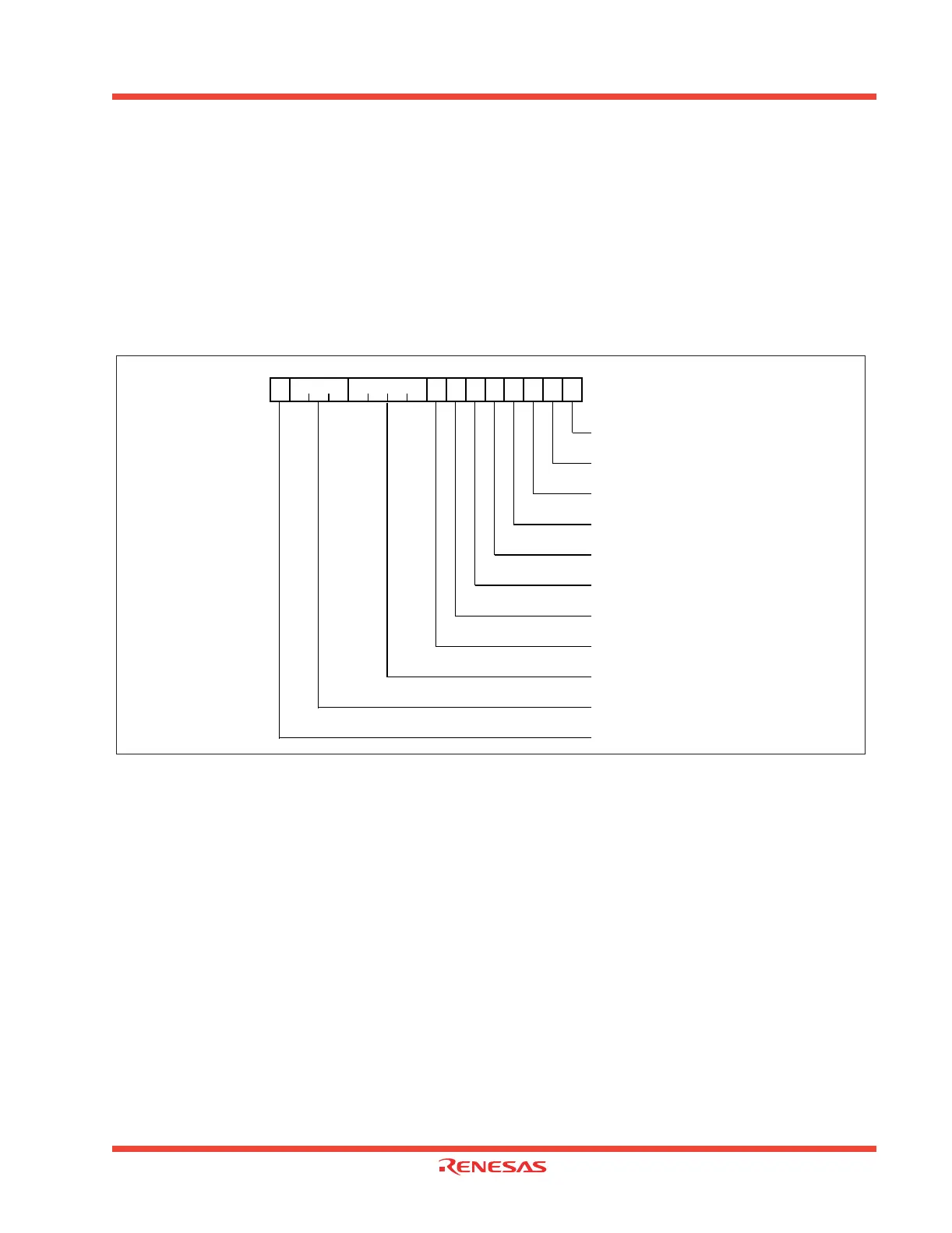

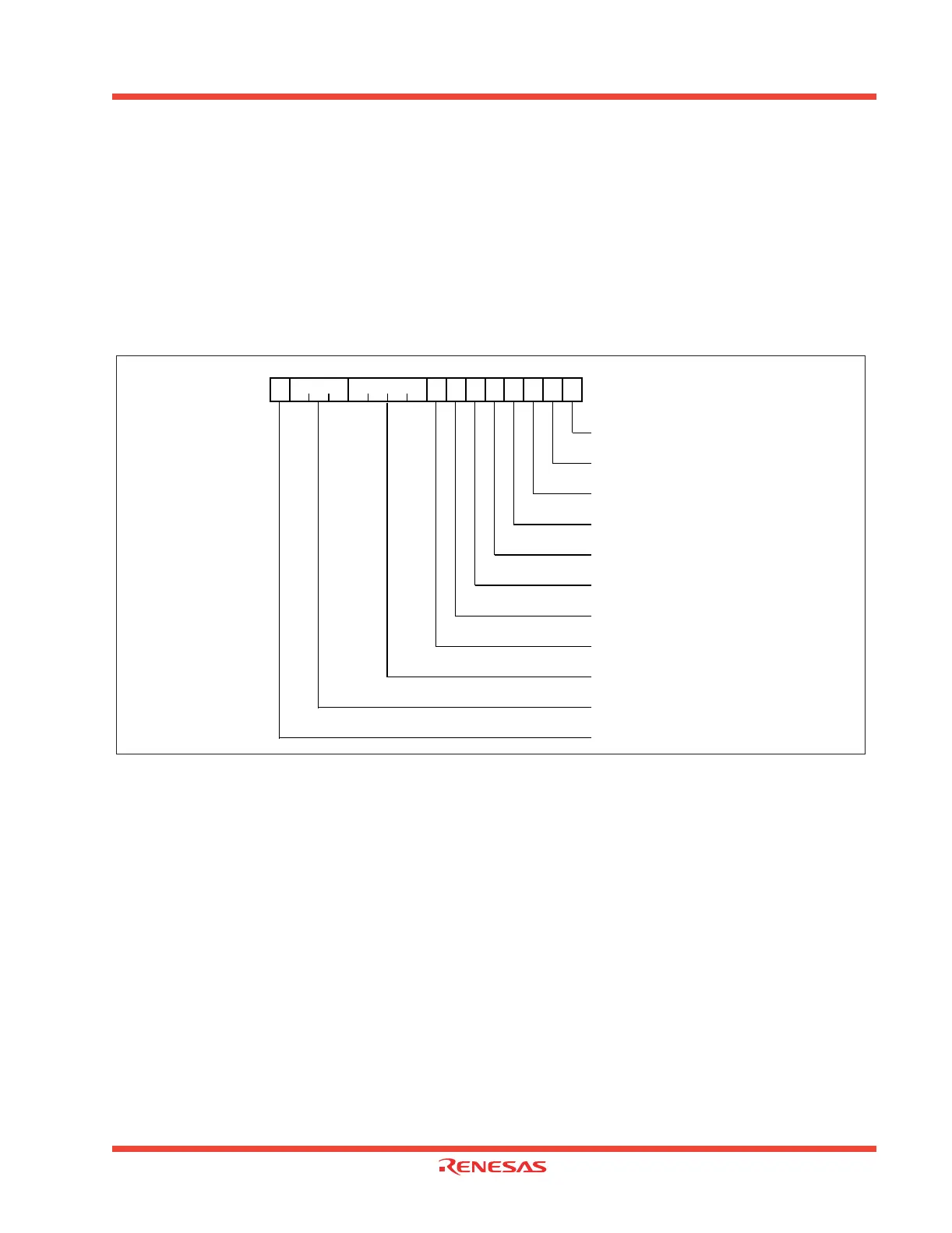

Figure 1.6: Flag register (FLG)

Carry flag

Debug flag

Zero flag

Sign flag

Register bank select flag

Overflow flag

Interrupt enable flag

Stack pointer select flag

Reserved area

Processor interrupt priori

Flag register (FLG)

CDZSBOIU

IPL

b0b15

Reserved area

Loading...

Loading...