Universal Serial Bus

M30240 Group

Rev.1.00 Sep 24, 2003 Page 303 of 360

• Receive an illegal data toggle during a STATUS stage,

• Receive an illegal data toggle during a SETUP stage,

• Host requests more data than specified during the SETUP stage (receive an IN token when the

DATA_END is set),

• Host sends more data then specified during the SETUP stage (receive an OUT token when the

DATA_END is set),

• Receive larger data packet than the maximum packet (MaxP) size.

All of the conditions stated (except bad data toggle in the SETUP stage) cause the device to send a

STALL handshake for the current IN/OUT transaction. For the bad data toggle in the SETUP state, the

device sends ACK for the SETUP stage and then sends STALL for the next IN/OUT transaction. A

STALL handshake caused by the above listed conditions lasts for one transaction and terminates the

ongoing control transfer. Any packet after the STALL handshake will be seen as the beginning of a

new control transfer.

The CPU writes a “0” to clear the FORCE_STALL status bit.

• SETUP_END Flag

This becomes “1” when processing is interrupted in mid course prior to the end of the transfer of the

data size set during the control transfer and data phase processing. This bit should be cleared to “0”

by writing “1” to the SERVICED_SETUP_END bit.Once the CPU detects the SETUP_END bit as set,

it should stop accessing the FIFO to service the previous setup transaction.

If this bit should become “1” and the OUT_PKT_RDY flag simultaneously becomes “1”, that would in-

dicate that the setup processing that was established earlier has been completed and that there is a

new SETUP token inside the FIFO.

• SERVICED_OUT_PKT_RDY Bit

The OUT_PKT_RDY is cleared to “0” when this bit is set to “1”.

• SERVICED_SETUP_END Bit

The SETUP_END bit is cleared to “0” when this bit is set to “1”.

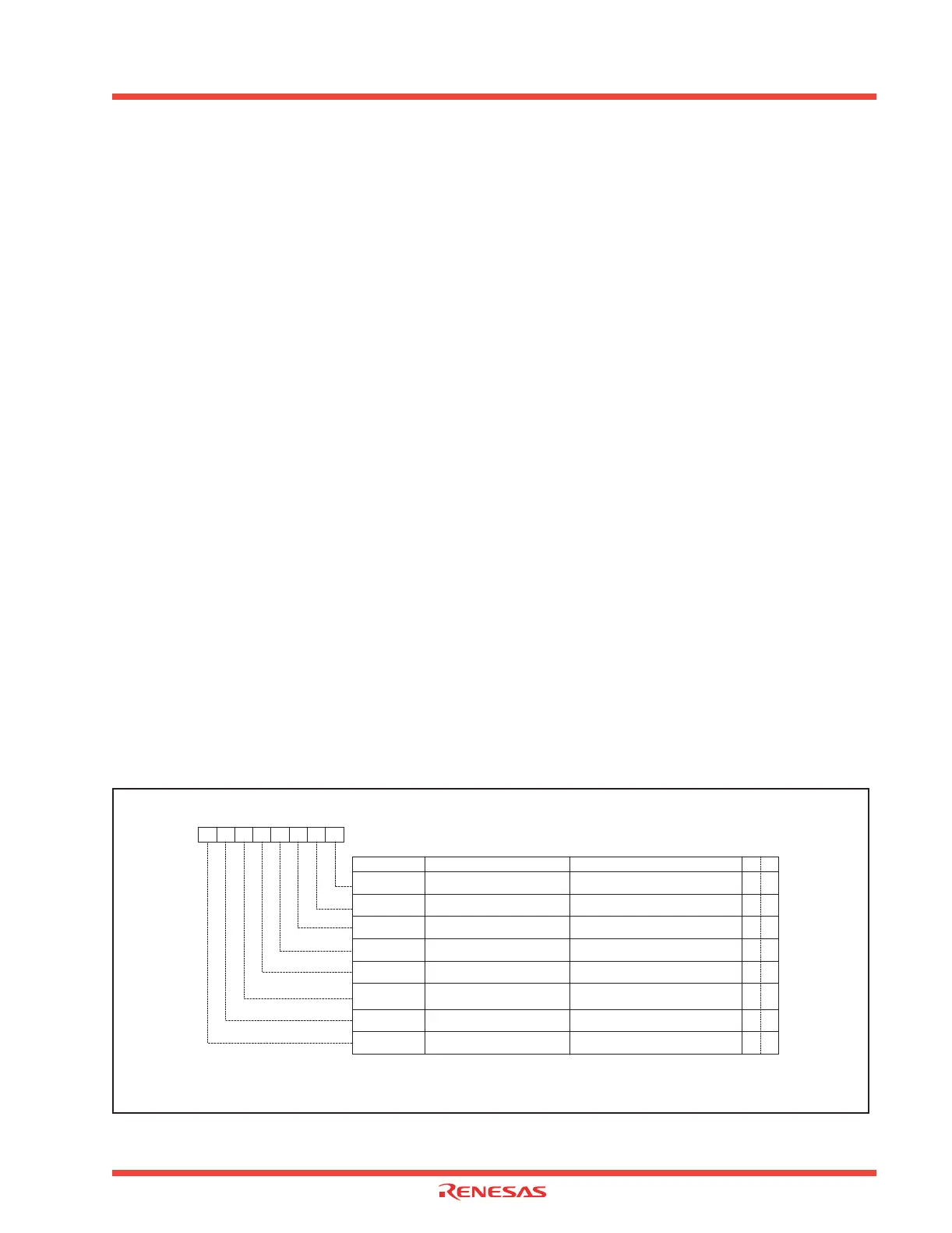

Figure 3.17 shows the structure of the USB Endpoint 0 Control/Status Register

Figure 3.17: USB Endpoint 0 Control/Status Register (EP0CS)

Bit Symbol Bit Name Function R W

EP0CSR0

OUT_PKT_RDY Flag

0: Not ready

1: Ready

O O

Symbol

EP0CS

Address

0311

16

When reset

00

16

USB Endpoint 0 Control and Status Register (Note 5)

b7 b5b6 b4 b3 b2 b1 b0

EP0CSR1

IN_PKT_RDY Bit

0: Not ready

1: Ready

O O

EP0CSR2 SEND_STALL Bit

0: No action

1: Stall Endpoint 0 by CPU

O O

Note 1

Note 2

Note 1: Read only

Note 2: Write "1" only or Read

Note 3: Write "0" only or Read

Note 4: Write only - Read "0"

Note 5: Refer to Programming Notes in Chapter 1, Section 5.5

EP0CSR3

DATA_END Bit

0: No action

1: Last packet transferred to/from FIFO

O O

EP0CSR4

FORCE_STALL Flag (Note 1)

0: No action

1: Stall Endpoint 0 by USB FCU

O O

EP0CSR5 SETUP_END Flag

0: No action

1: Control transfer ended before specific

data length transferred during data phase

O O

Note 3

Note 1

EP0CSR6

SERVICED_OUT_PKT_RDY Bit

0: No change

1: Clear OUT_PKT_RDY bit

EP0CSR7

SERVICED_SETUP_END Bit

0: No change

1: Clear SETUP_END bit

Note 4

Note 4

Note 2

O O

O O

Loading...

Loading...