RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1128

Dec 10, 2015

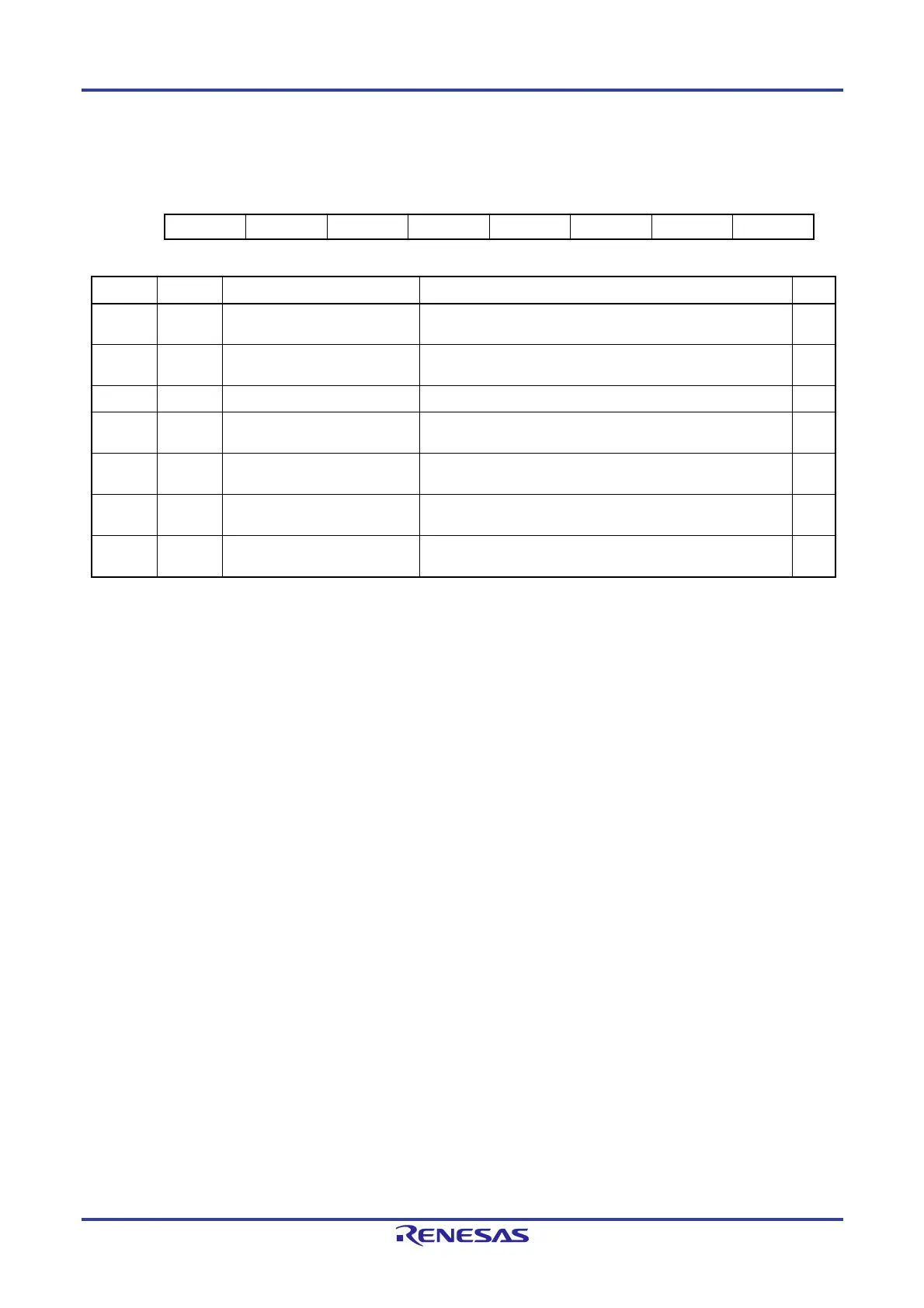

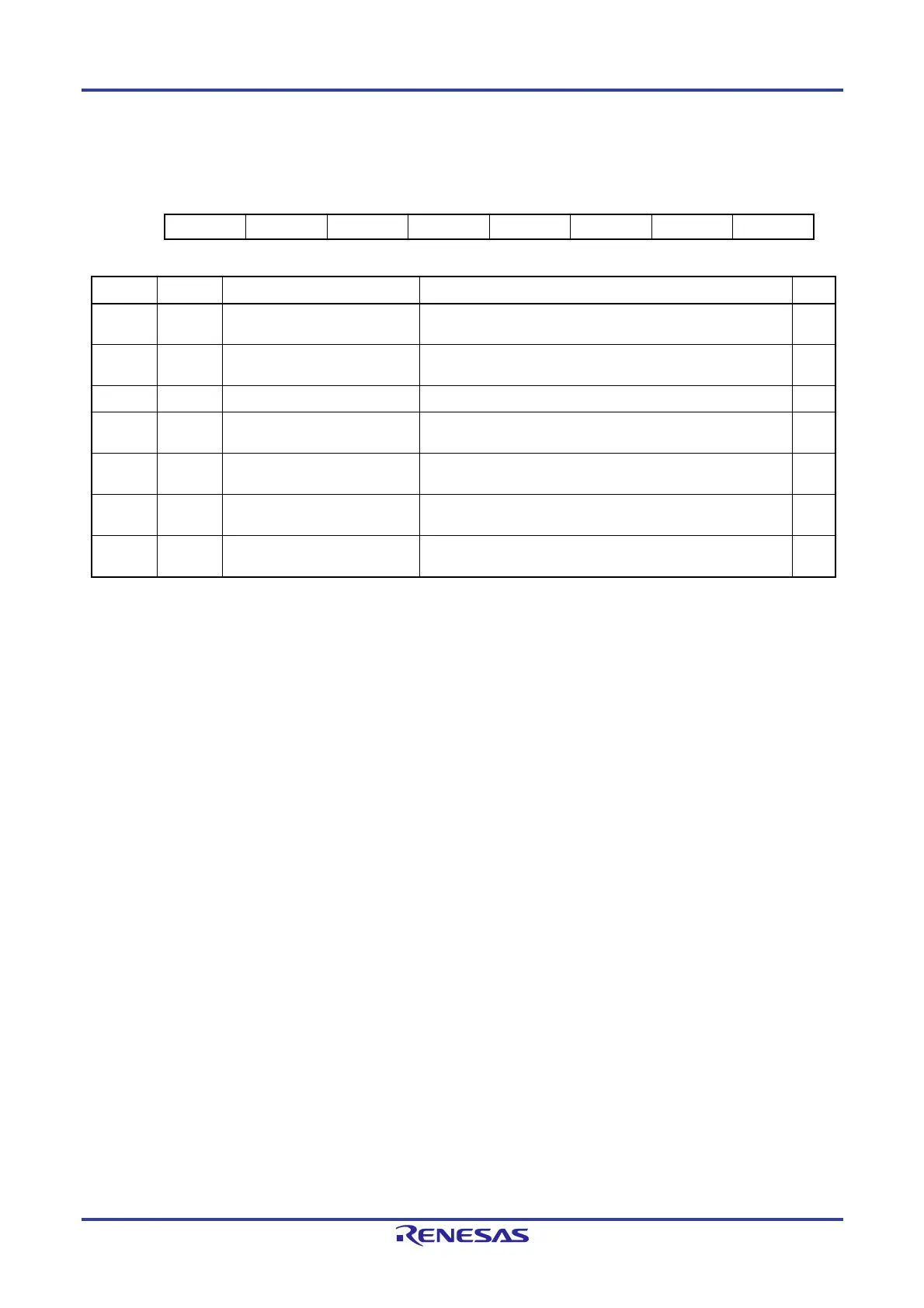

(19) LIN/UART Status Register (LSTn)

Address: F06D2H

7 6 5 4 3 2 1 0

HTRC D1RC — — ERR — FRC FTC

Value after reset:

0 0 0 0 0 0 0 0

Bit Symbol Bit Name Function R/W

0 FTC Successful Frame/Wake-up

Transmission Flag

0: Frame or wake-up transmission has not been completed.

1: Frame or wake-up transmission has been completed.

R/W

1 FRC Successful Frame/Wake-up

Reception Flag

0: Frame or wake-up reception has not been completed.

1: Frame or wake-up reception has been completed.

R/W

2 — Reserved This bit is always read as 0. The write value should always be 0. R/W

3 ERR Error Detection Flag 0: No error has been detected.

1: Error has been detected.

R

4, 5 — Reserved These bits are always read as 0. The write value should always

be 0.

R/W

6 D1RC Successful Data 1 Reception

Flag

0: Data 1 reception has not been completed.

1: Data 1 reception has been completed.

R/W

7 HTRC Successful Header Transmission

Flag

0: Header transmission has not been completed.

1: Header transmission has been completed.

R/W

The LSTn register is automatically cleared to 00H upon transition to LIN reset mode and start of the next communication

(the FTS bit in the LTRCn register is 1).

In LIN reset mode, writing to this register is disabled. In LIN reset mode, the register retains 00H.

To clear the specific bits in the register, write 0 to the bits to be cleared and write 1 to the other bits by using an 8-bit data

transfer instruction.

FTC flag (successful frame/wake-up transmission flag)

Only 0 can be written to the FTC flag; when 1 is written, the bit retains the value that has been retained before 1 is written.

The FTC flag is set to 1 upon completion of response or wake-up transmission. Here, an interrupt is generated if the FTCIE

bit in the LIEn register is 1 (interrupt is enabled). To clear the bit to 0 before the next communication (the FTS bit in the

LTRCn register is 1), write 0 to the bit in LIN operation mode or LIN wake-up mode.

When response data of 9 bytes or more is to be transmitted, this bit is set to 1 each time a data group (variable from 0 to 8

bytes) is transmitted. Write 0 before starting transmission of the next data group.

FRC flag (successful frame/wake-up reception flag)

Only 0 can be written to the FRC flag; when 1 is written, the bit retains the value that has been retained before 1 is written.

The FRC flag is set to 1 upon completion of response or wake-up reception. Here, an interrupt is generated if the FRCIE bit

in the LIEn register is 1 (interrupt is enabled). To clear the bit to 0 before the next communication (the FTS bit in the LTRCn

register is 1), write 0 to the bit in LIN operation mode or LIN wake-up mode.

When response data of 9 bytes or more is to be received, this bit is set to 1 each time a data group (variable from 0 to 8

bytes) is received. Write 0 before starting reception of the next data group.

Loading...

Loading...