RL78/F13, F14 CHAPTER 17 LIN/UART MODULE (RLIN3)

R01UH0368EJ0210 Rev.2.10 1162

Dec 10, 2015

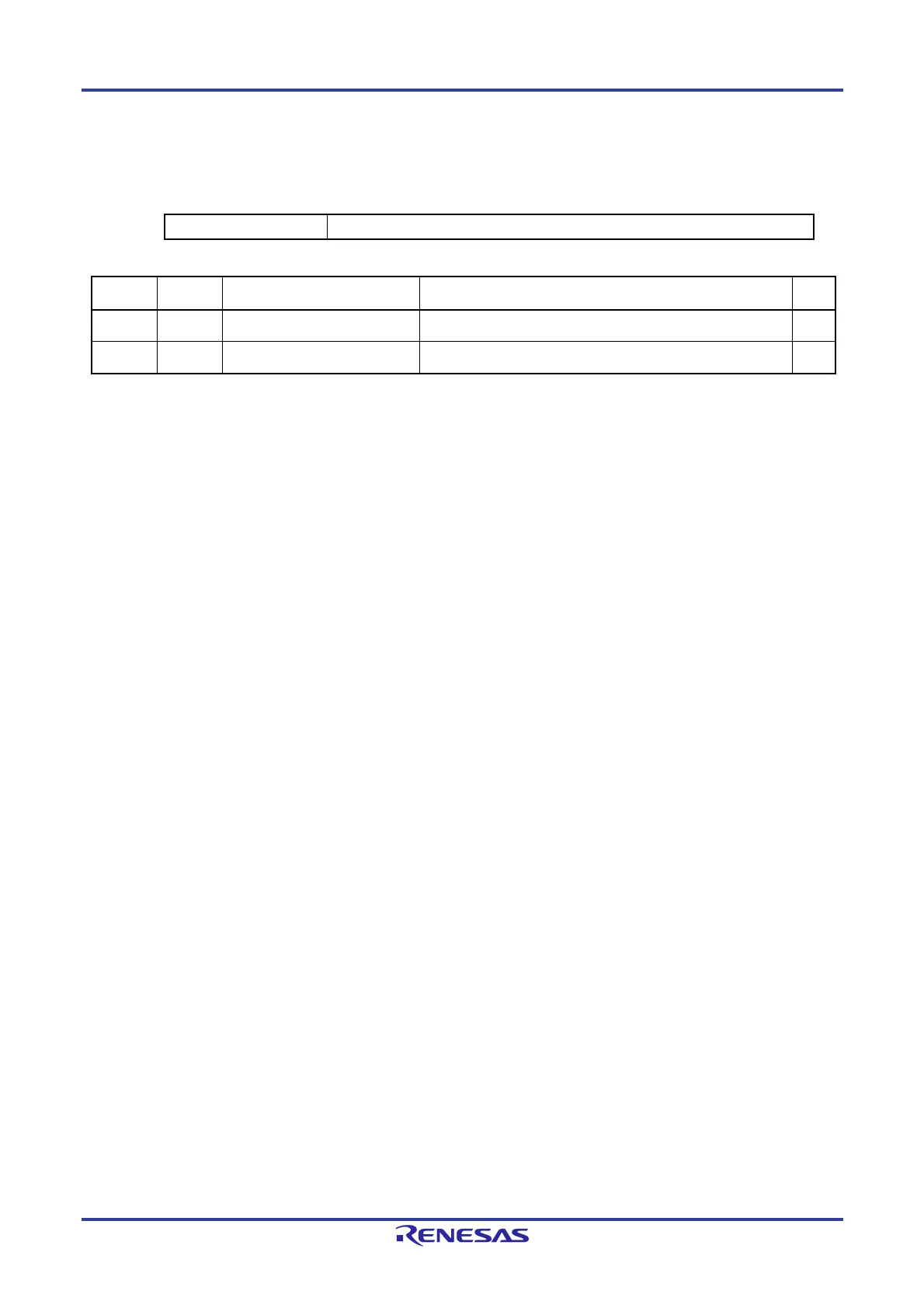

(21) LIN/UART ID Buffer Register (LIDBn)

Address: F06D5H

7 6 5 4 3 2 1 0

IDP[1:0] ID[5:0]

Value after reset:

0 0 0 0 0 0 0 0

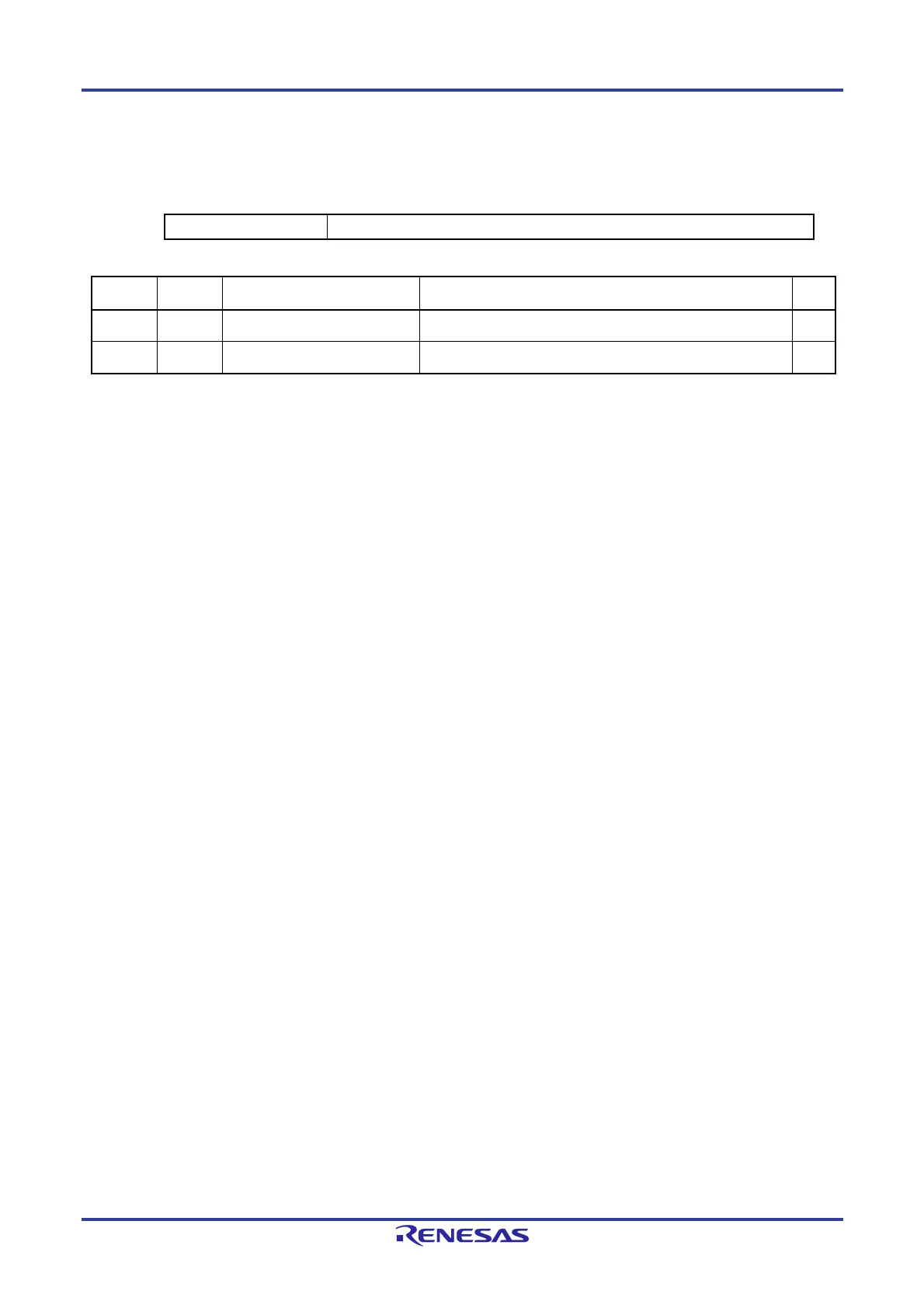

Bit Symbol Bit Name Function R/W

5 to 0 ID[5:0] ID Holds the 6-bit ID value received in the ID field. R/W

7, 6 IDP[1:0] Parity Holds the parity bits (P) received in the ID field. R/W

Writing to the LIDBn register is enabled upon completion of header reception.

In LIN mode (LIN operation mode or LIN wake-up mode), writing is disabled.

In LIN self-test mode, this register operates as follows:

Write the value to be transmitted before communication. The reversed value of the value received can be read from the

register after frame transmission/reception is completed (after loopback).

For details of LIN self-test mode, refer to 17.6 LIN Self-Test Mode.

ID[5:0] bits (ID bits)

The ID bits hold the 6-bit ID value received in the ID field of the LIN frame.

IDP[1:0] bits (parity bits)

The IDP bits hold the parity bits (P0 and P1) received in the ID field of the LIN frame.

The IDP0 bit is P0 and the IDP1 bit is P1.

When the IPERE bit in the LEDEn register is 1 (ID parity detection is enabled), the received value is checked against the

internally pre-calculated value, and if they do not agree, the IPER bit (ID parity error flag) is set.

Loading...

Loading...