RL78/F13, F14 CHAPTER 27 SAFETY FUNCTIONS

R01UH0368EJ0210 Rev.2.10 1604

Dec 10, 2015

<Control register>

Invalid memory access detection control register (IAWCTL)

This register is used to control the detection of invalid memory access and RAM/SFR guard function.

IAWEN bit is used in invalid memory access detection function.

The IAWCTL register can be set by an 8-bit memory manipulation instruction.

Reset signal generation clears this register to 00H.

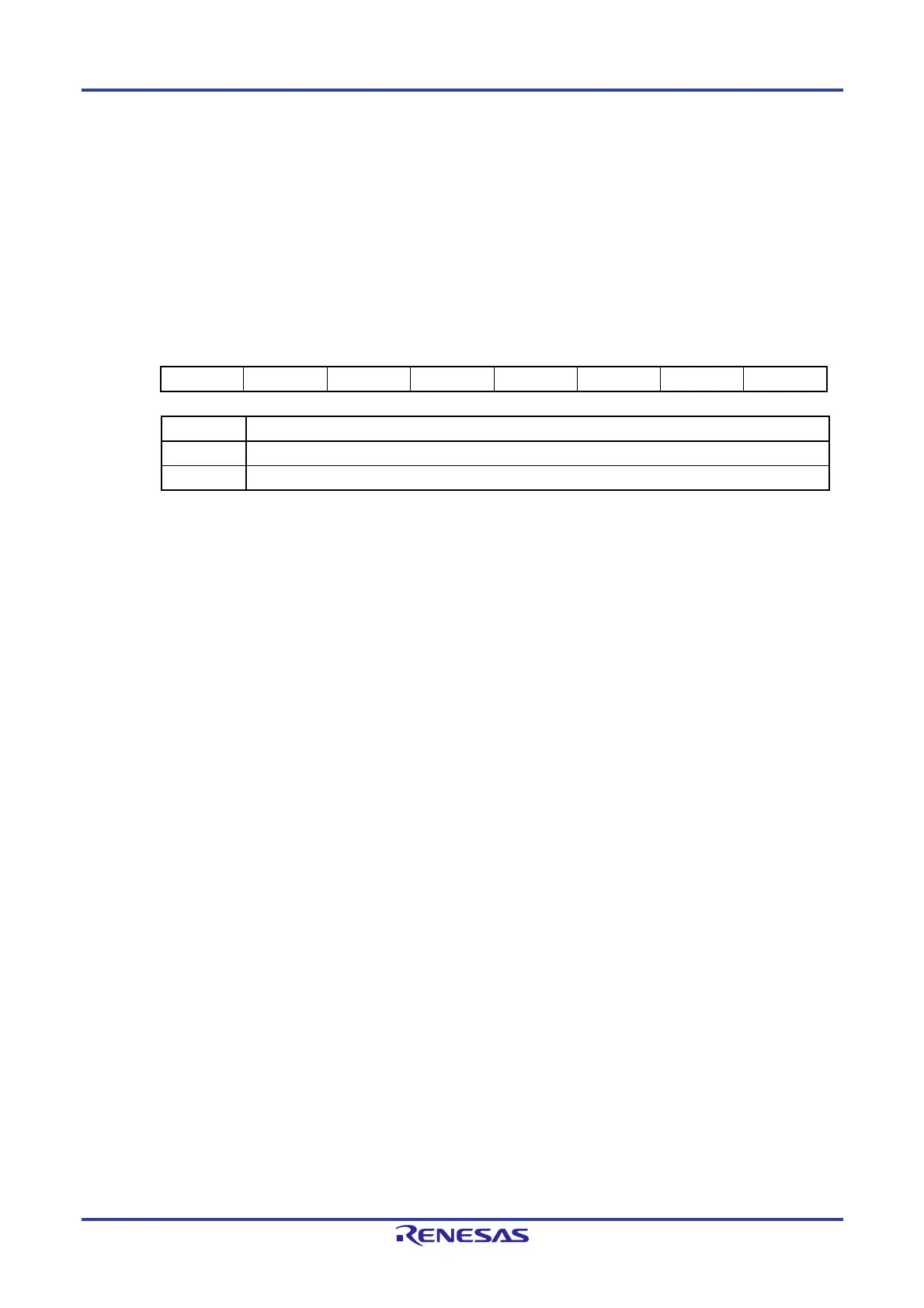

Figure 27-22. Format of Invalid Memory Access Detection Control Register (IAWCTL)

Address: F0078H After reset: 00H R/W

Symbol 7 6 5 4 3 2 1 0

IAWCTL IAWEN 0 GRAM1 GRAM0 0 GPORT GINT GCSC

IAWEN

Note

Control of invalid memory access detection

0 Disable the detection of invalid memory access.

1 Enable the detection of invalid memory access.

Remark By specifying WDTON = 1 for the option byte, the invalid memory access function is always enabled

regardless of the setting for the IAWEN bit. (For details, see CHAPTER 29 OPTION BYTE.)

Note Only writing 1 to the IAWEN bit is valid, and writing 0 after setting the IAWEN bit to 1 is invalid.

Loading...

Loading...