RL78/F13, F14 CHAPTER 3 CPU ARCHITECTURE

R01UH0368EJ0210 Rev.2.10 164

Dec 10, 2015

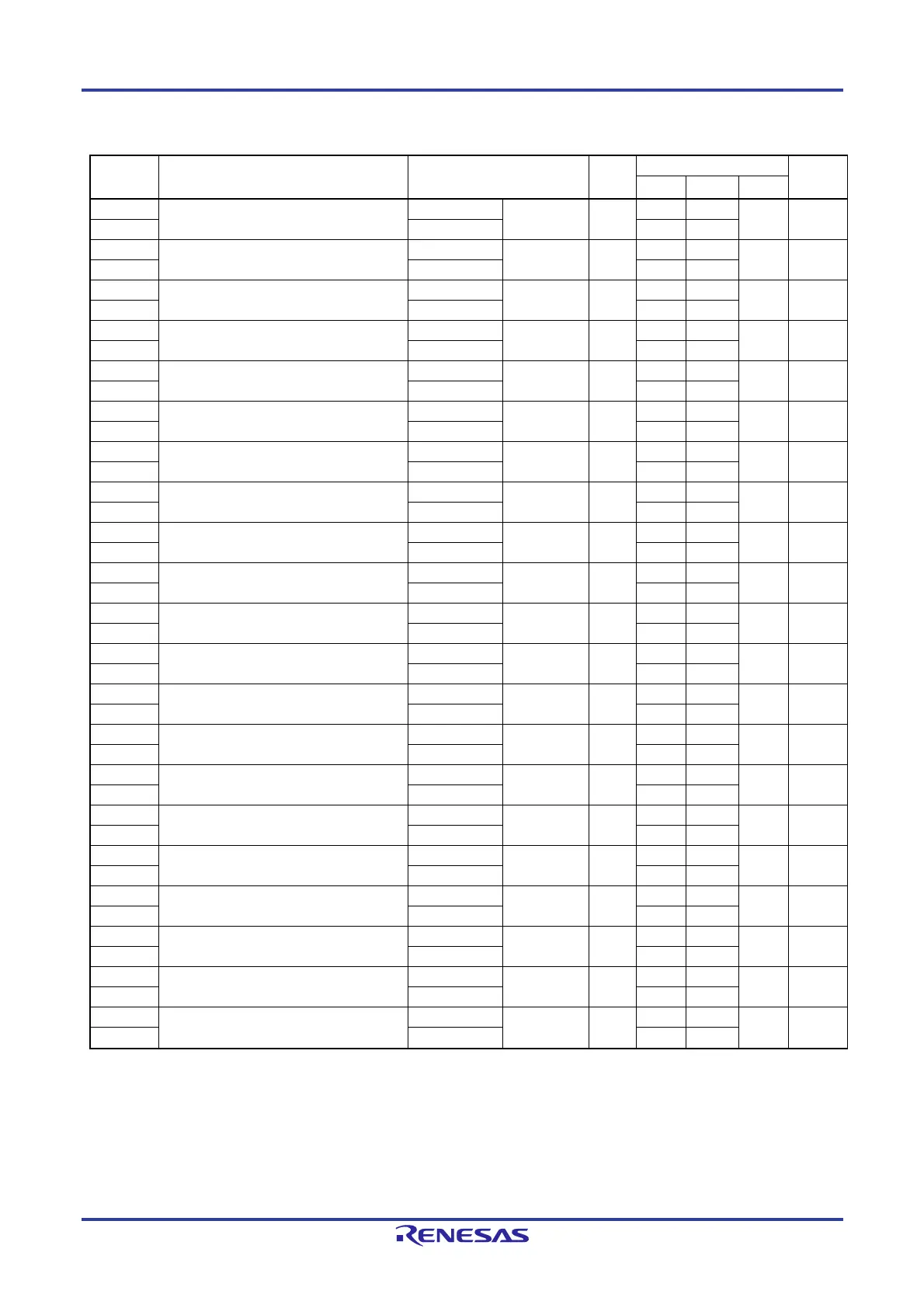

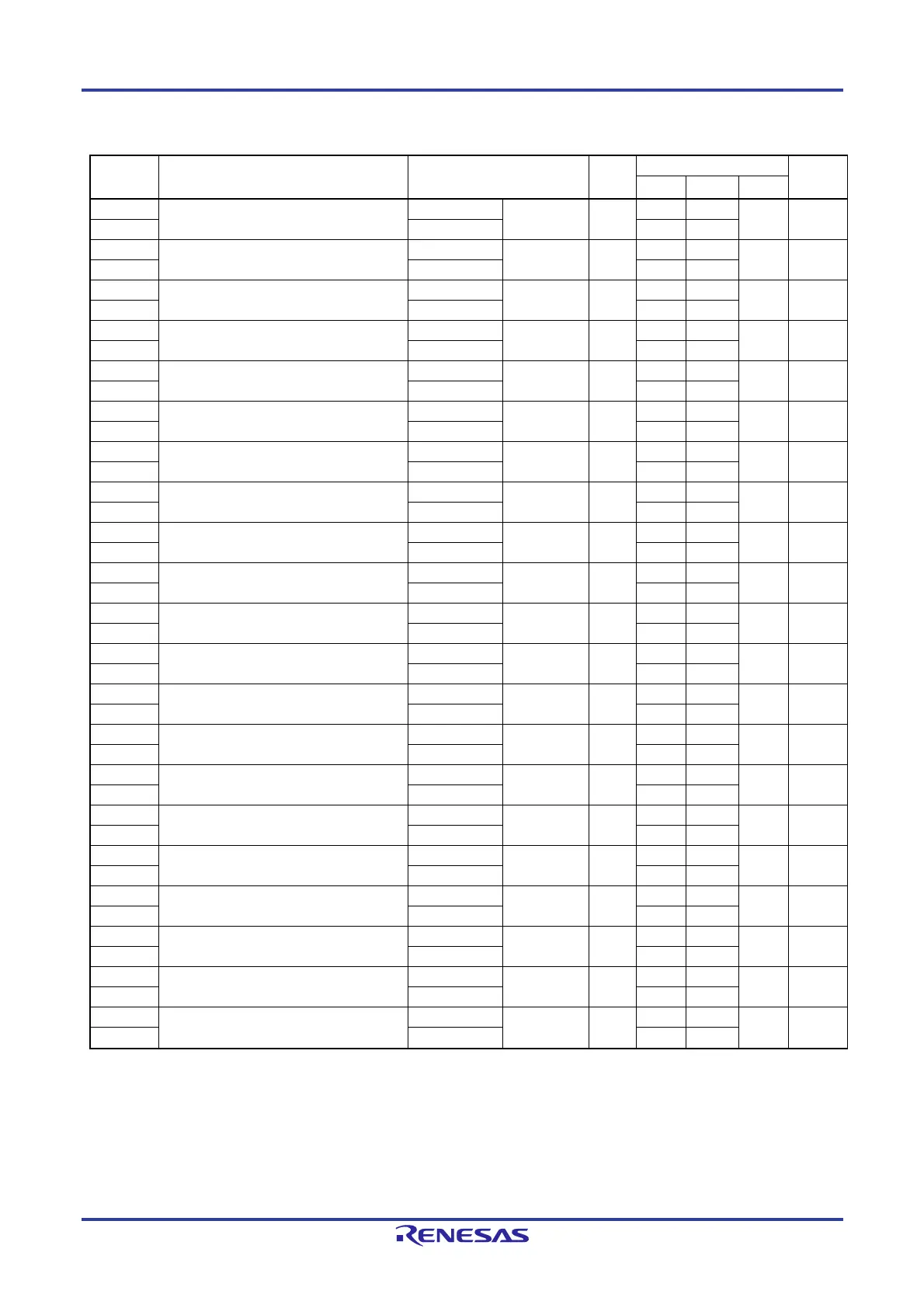

Table 3-6. Extended SFR (2nd SFR) List (13/32)

Address Special Function Register (2nd SFR)

Name

Symbol R/W Manipulable Bit Range After

reset

1-bit 8-bit 16-bit

F03B0H CAN receive buffer register 1AL

Note 2

RMIDL1L RMIDL1 R – √ √ 0000H

F03B1H RMIDL1H – √

F03B2H CAN receive rule entry register 1BH

Note 1

GAFLMH1L GAFLMH1 R/W – √ √ 0000H

F03B3H GAFLMH1H – √

F03B2H CAN receive buffer register 1AH

Note 2

RMIDH1L RMIDH1 R – √ √ 0000H

F03B3H RMIDH1H – √

F03B4H CAN receive rule entry register 1CL

Note 1

GAFLPL1L GAFLPL1 R/W – √ √ 0000H

F03B5H GAFLPL1H – √

F03B4H CAN receive buffer register 1BL

Note 2

RMTS1L RMTS1 R – √ √ 0000H

F03B5H RMTS1H – √

F03B6H CAN receive rule entry register 1CH

Note 1

GAFLPH1L GAFLPH1 R/W – √ √ 0000H

F03B7H GAFLPH1H – √

F03B6H CAN receive buffer register 1BH

Note 2

RMPTR1L RMPTR1 R – √ √ 0000H

F03B7H RMPTR1H – √

F03B8H CAN receive rule entry register 2AL

Note 1

GAFLIDL2L GAFLIDL2 R/W – √ √ 0000H

F03B9H GAFLIDL2H – √

F03B8H CAN receive buffer register 1CL

Note 2

RMDF01L RMDF01 R – √ √ 0000H

F03B9H RMDF01H – √

F03BAH CAN receive rule entry register 2AH

Note 1

GAFLIDH2L GAFLIDH2 R/W – √ √ 0000H

F03BBH GAFLIDH2H – √

F03BAH CAN receive buffer register 1CH

Note 2

RMDF11L RMDF11 R – √ √ 0000H

F03BBH RMDF11H – √

F03BCH CAN receive rule entry register 2BL

Note 1

GAFLML2L GAFLML2 R/W – √ √ 0000H

F03BDH GAFLML2H – √

F03BCH CAN receive buffer register 1DL

Note 2

RMDF21L RMDF21 R – √ √ 0000H

F03BDH RMDF21H – √

F03BEH CAN receive rule entry register 2BH

Note 1

GAFLMH2L GAFLMH2 R/W – √ √ 0000H

F03BFH GAFLMH2H – √

F03BEH CAN receive buffer register 1DH

Note 2

RMDF31L RMDF31 R – √ √ 0000H

F03BFH RMDF31H – √

F03C0H CAN receive rule entry register 2CL

Note 1

GAFLPL2L GAFLPL2 R/W – √ √ 0000H

F03C1H GAFLPL2H – √

F03C0H CAN receive buffer register 2AL

Note 2

RMIDL2L RMIDL2 R – √ √ 0000H

F03C1H RMIDL2H – √

F03C2H CAN receive rule entry register 2CH

Note 1

GAFLPH2L GAFLPH2 R/W – √ √ 0000H

F03C3H GAFLPH2H – √

F03C2H CAN receive buffer register 2AH

Note 2

RMIDH2L RMIDH2 R – √ √ 0000H

F03C3H RMIDH2H – √

F03C4H CAN receive rule entry register 3AL

Note 1

GAFLIDL3L GAFL1DL3 R/W – √ √ 0000H

F03C5H GAFLIDL3H – √

F03C4H CAN receive buffer register 2BL

Note 2

RMTS2L RMTS2 R – √ √ 0000H

F03C5H RMTS2H

– √

Notes 1. These registers are allocated to the RAM window 0 for the CAN module (receive rule and CAN RAM test register).

When setting these registers, set the RPAGE bit in the GRWCR register to 0.

2. These registers are allocated to the RAM window 1 for the CAN module (receive buffer, receive FIFO buffer,

transmit/receive FIFO buffer, transmit buffer, and transmit history data). When setting these registers, set the

RPAGE bit in the GRWCR register to 1.

Loading...

Loading...