RL78/F13, F14 CHAPTER 5 CLOCK GENERATOR

R01UH0368EJ0210 Rev.2.10 414

Dec 10, 2015

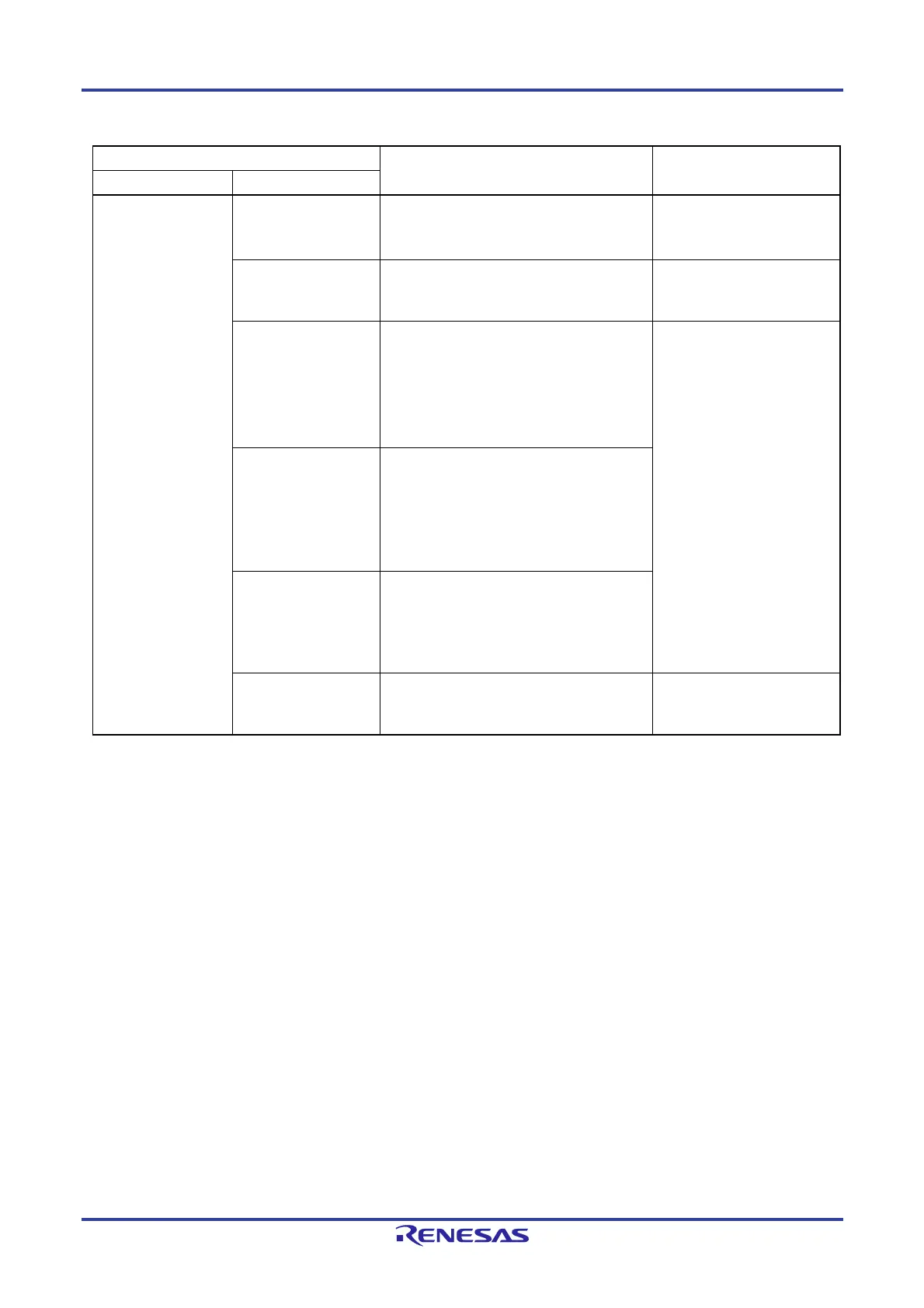

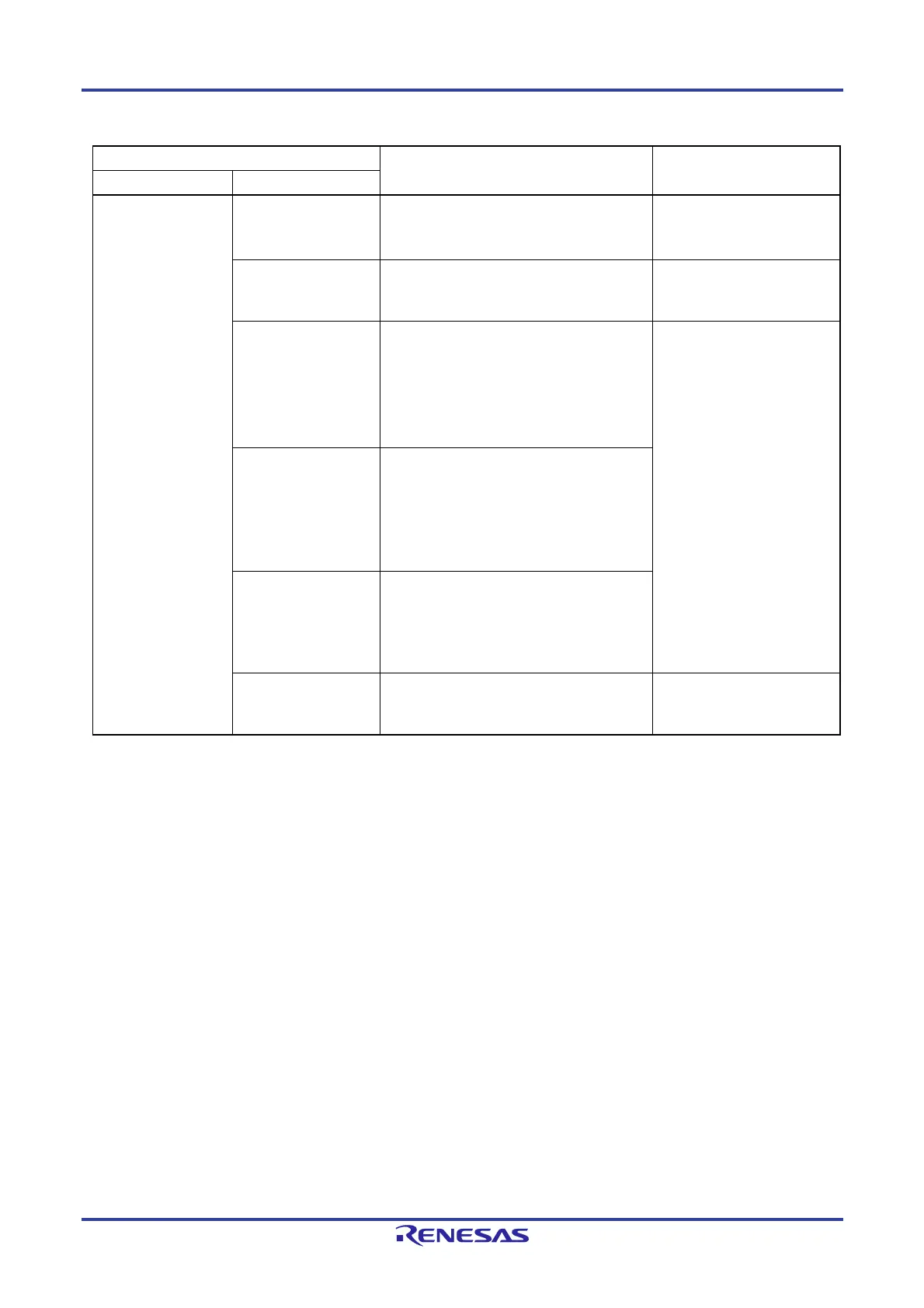

Table 5-3. Changing CPU Clock (2/7)

CPU Clock Conditions before Change Processing after Change

Before Change After Change

X1 clock

High-speed on-chip

oscillator clock

The high-speed on-chip oscillator starts

oscillation.

HIOSTOP = 0

X1 oscillation can be stopped.

(MSTOP = 1)

External main system

clock

Prohibited to change. (To change the CPU

clock, clear the settings first and then reset the

settings.)

XT1 clock

XT1 oscillation is stable, and the subsystem

clock is selected as the subsystem/low-speed

on-chip oscillator select clock.

OSCSELS = 1, EXCLKS = 0, XTSTOP = 0

SELLOSC = 0

After elapse of oscillation stabilization time

X1 oscillation can be stopped.

(MSTOP = 1)

External subsystem

clock

External clock input from the EXCLKS pin is

enabled, and the subsystem clock is selected

as the subsystem/low-speed on-chip oscillator

select clock.

OSCSELS = 1, EXCLKS = 1, XTSTOP = 0

SELLOSC = 0

Low-speed on-chip

oscillator clock

The low-speed on-chip oscillator starts

oscillation, and the low-speed on-chip oscillator

clock is selected as the subsystem/low-speed

on-chip oscillator select clock.

OSCSELS = 1, SELLOSC = 1

PLL clock PLL oscillation is stable.

LOCK = 1, PLLON = 1

The X1 clock cannot be

stopped because it is the PLL

input clock.

Remark For details about the register flag settings for stopping the target clock during the processing after change and

conditions before the clock is stopped, see 5.6.9 Conditions Before Clock Oscillation Is Stopped.

Loading...

Loading...