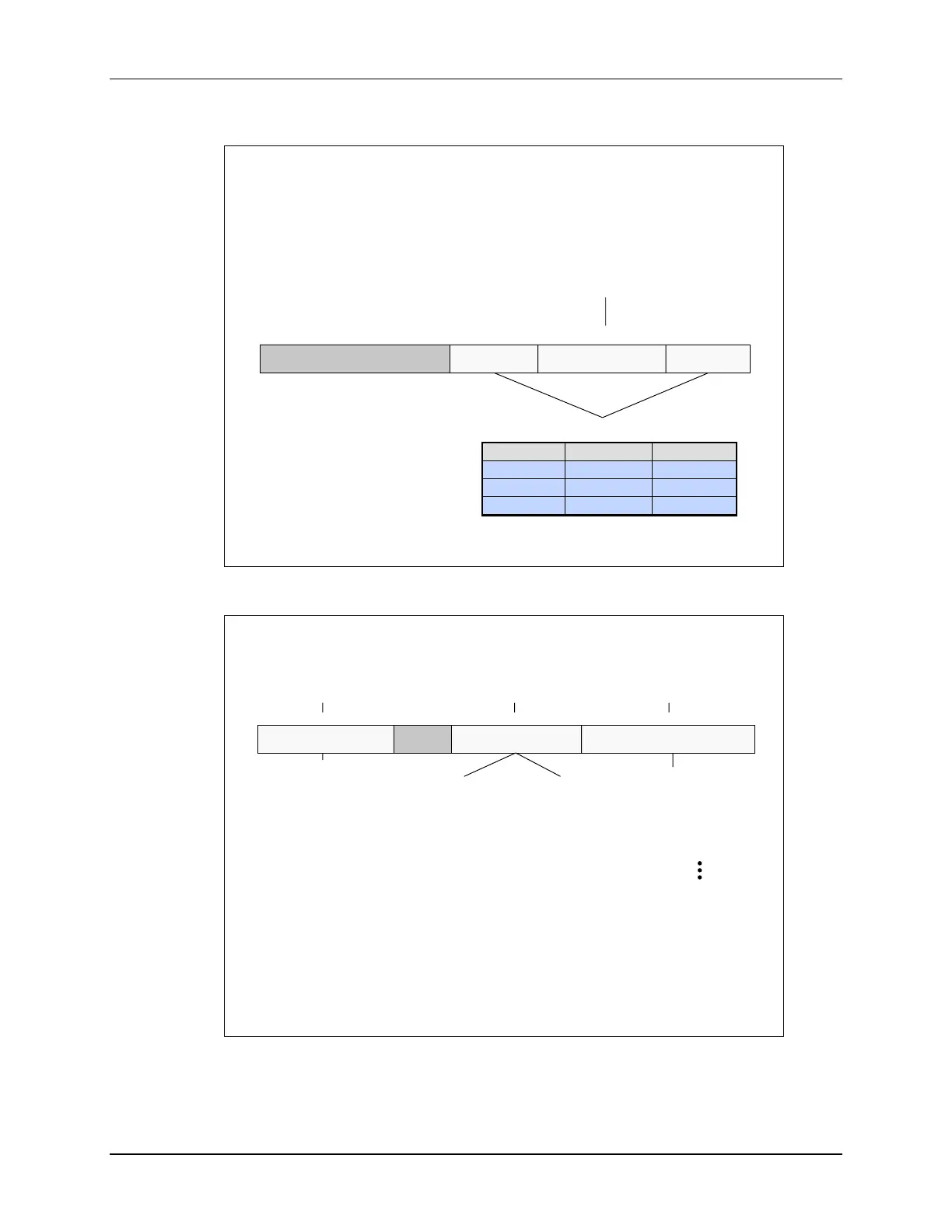

ADC Control Register 2

AdcRegs.ADCCTL2

reserved

15 - 3

2 0

CLKDIV4EN CLKDIV2EN

ADCNONOVERLAP

1

ADC Clock Divider

CLKDIV4EN CLKDIV2EN ADCCLK

x 0 SYSCLK

0 1 SYSCLK / 2

1 1 SYSCLK / 4

ADC Overlap Bit

0 = overlap of sample and conversion is allowed

1 = overlap of sample is not allowed

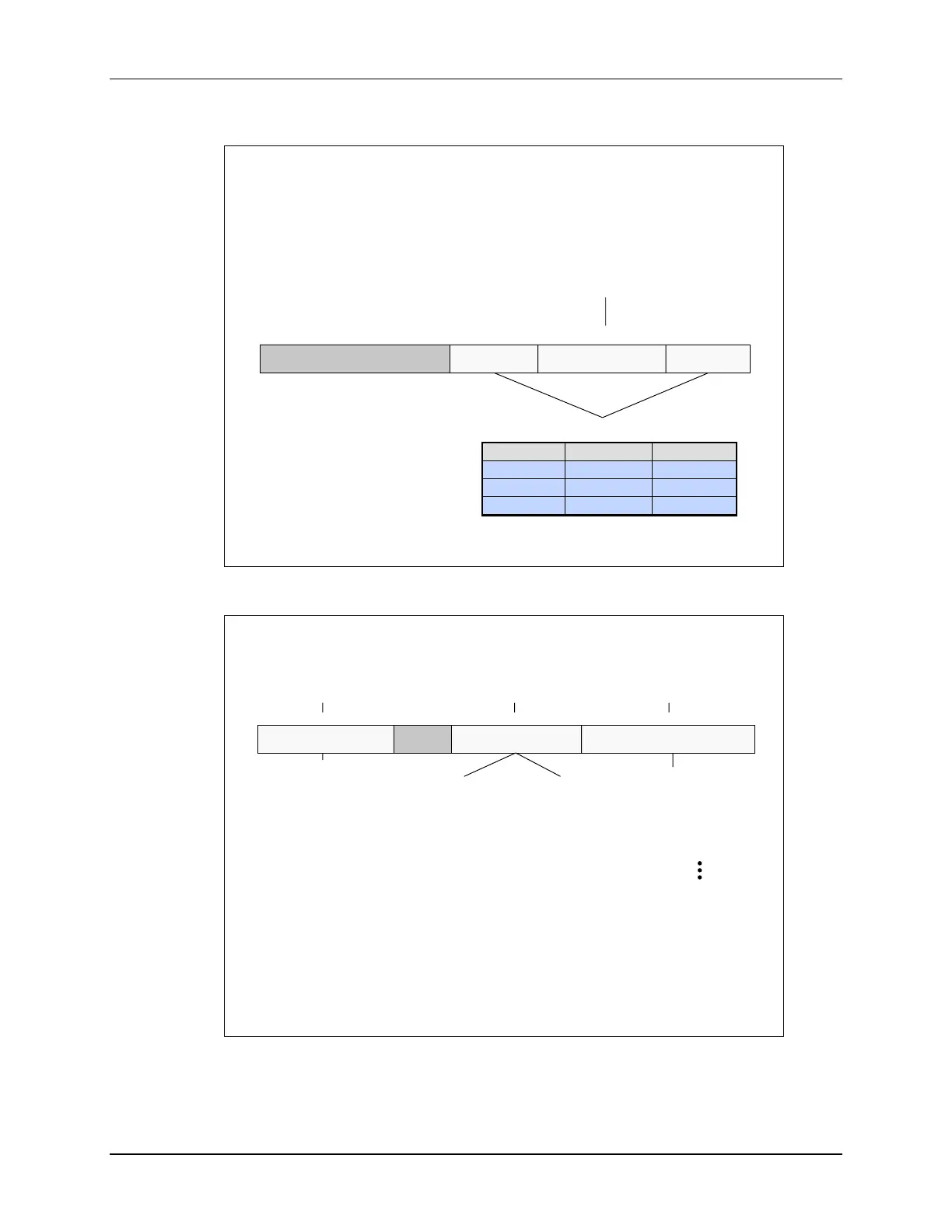

ADC SOC0 – SOC15 Control Registers

AdcRegs.ADCSOCxCTL

TRIGSEL reserved

15 - 11

10 9 - 6 5 - 0

CHSEL ACQPS

SOCx Trigger

Source Select

SOCx Channel

Select

SOCx Acquisition

Prescale

(S/H window)

0h = ADCINA0 0h = ADCINA0/B0

1h = ADCINA1 1h = ADCINA1/B1

2h = ADCINA2 2h = ADCINA2/B2

3h = ADCINA3 3h = ADCINA3/B3

4h = ADCINA4 4h = ADCINA4/B4

5h = ADCINA5 5h = ADCINA5/B5

6h = ADCINA6 6h = ADCINA6/B6

7h = ADCINA7 7h = ADCINA7/B7

8h = ADCINB0 8h – Fh = invalid

9h = ADCINB1

Ah = ADCINB2

Bh = ADCINB3

Ch = ADCINB4

Dh = ADCINB5

Eh = ADCINB6

Fh = ADCINB7

Sequential S/M

(SIMULENx=0)

Simultaneous S/M

(SIMULENx=1)

00h = software

01h = CPU Timer 0

02h = CPU Timer 1

03h = CPU Timer 2

04h = XINT2SOC

05h = ePWM1SOCA

06h = ePWM1SOCB

07h = ePWM2SOCA

08h = ePWM2SOCB

09h = ePWM3SOCA

0Ah = ePWM3SOCB

0Bh = ePWM4SOCA

0Ch = ePWM4SOCB

0Dh = ePWM5SOCA

0Eh = ePWM5SOCB

0Fh = ePWM6SOCA

10h = ePWM6SOCB

11h = ePWM7SOCA

12h = ePWM7SOCB

13h = ePWM8SOCA

14h = ePWM8SOCB

00h – 05h = invalid

06h = 7 cycles long

07h = 8 cycles long

08h = 9 cycles long

09h = 10 cycles long

3Fh = 64 cycles long

Sampling Window

Loading...

Loading...