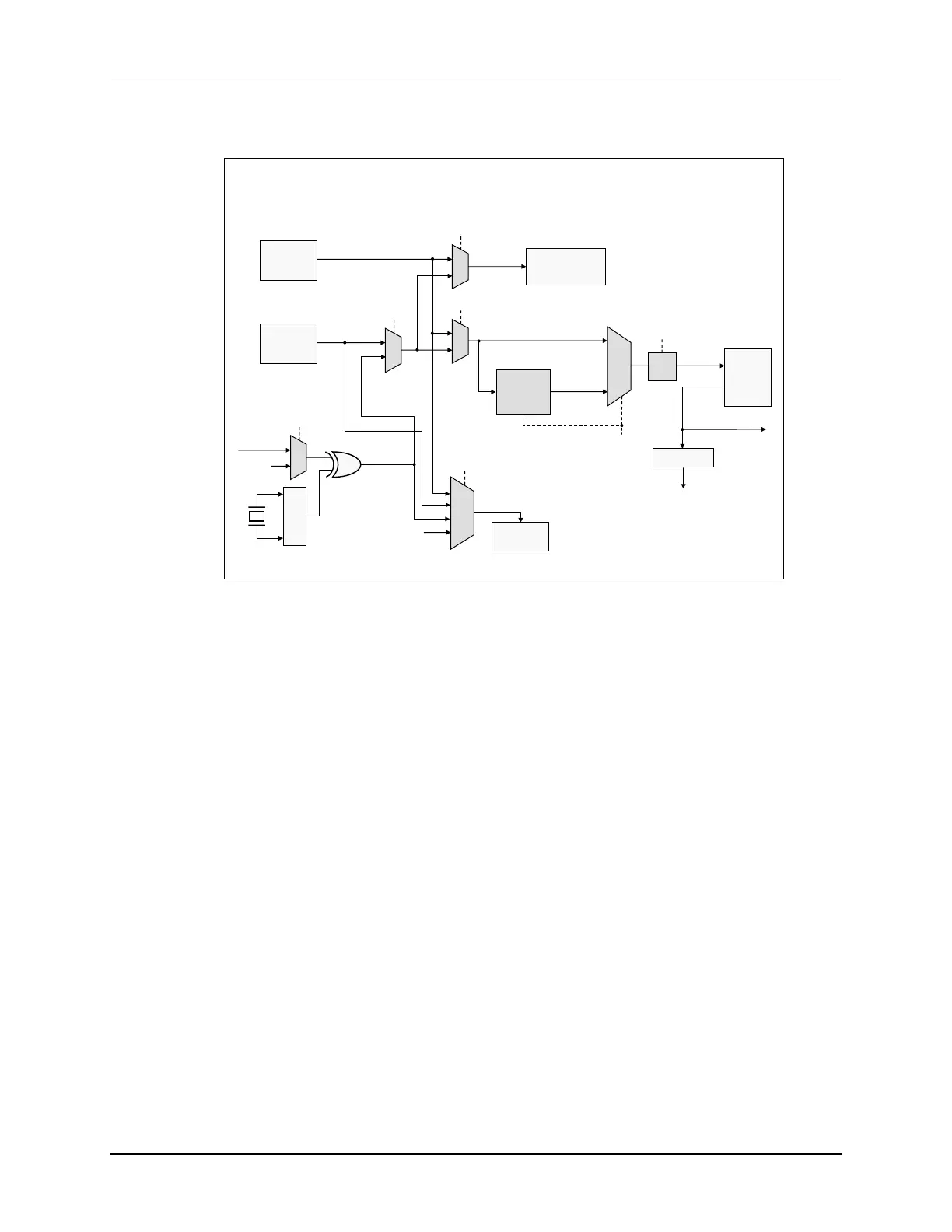

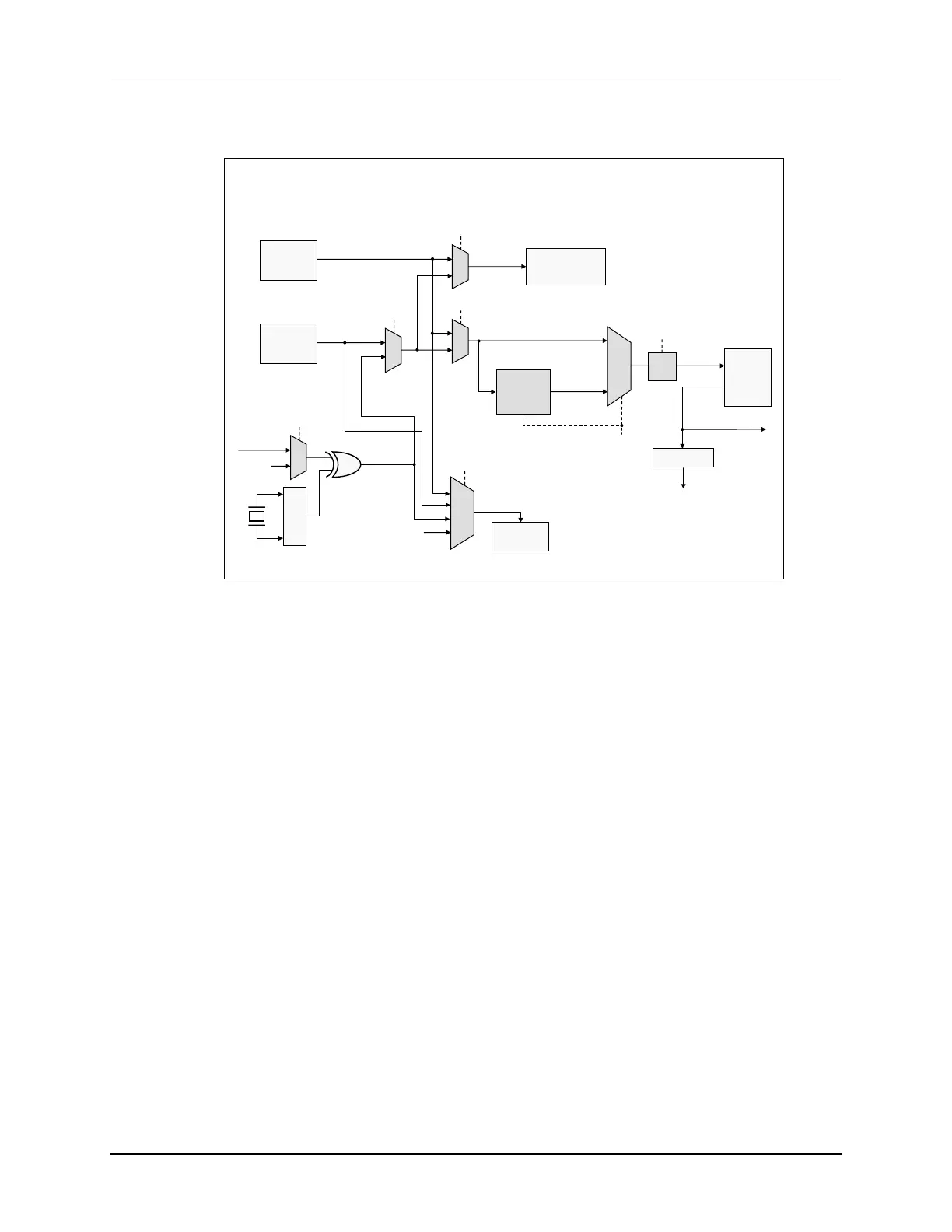

Oscillator/PLL Clock Module

C2000 Microcontroller Workshop - System Initialization 5 - 3

Oscillator/PLL Clock Module

F2806x Oscillator / PLL Clock Module

(lab file: SysCtrl.c)

XCLKINOFF

X2

XTAL OSC

X1

XTAL

0*

1

0

XCLKIN

Internal

OSC 1

(10 MHz)

Internal

OSC 2

(10 MHz)

OSCCLKSRC2

0*

1

WDCLKSRCSEL

0*

1

OSCCLKSRCSEL

0*

1

10

11

01

00*

CPU

Timer 2

SYSCLKOUT

TMR2CLKSRCSEL

PLL

VCOCLK

OSCCLK

C28x

Core

CLKIN

SYSCLKOUT

LOSPCP

LSPCLK

(PLL bypass)

LSPCLK

DIV

SCI, SPI

All other peripherals

clocked by SYSCLKOUT

MUX

1/n

DIVSEL

OSC1CLK

OSC2CLK

EXTCLK

Watchdog

Module

WDCLK

CPUTMR2CLK

* = default

The oscillator/PLL clock module has two internal, 10 MHz oscillators, and the availability of an

external oscillator or crystal. This provides redundancy in case an oscillator fails, as well as the

ability to use multiple oscillators. The asterisks in the multiplexers show the default settings.

This module has the capability to clock the watchdog, core, and CPU timer 2 from independent

clock sources, if needed.

The on-chip oscillator and phase-locked loop (PLL) block provide all the necessary clocking

signals for the F2806x devices. The two internal oscillators (INTOSC1 and INTOSC2) need no

external components.

Loading...

Loading...