Phaser 3300MFP Service Manual 2-25

Theory of Operation

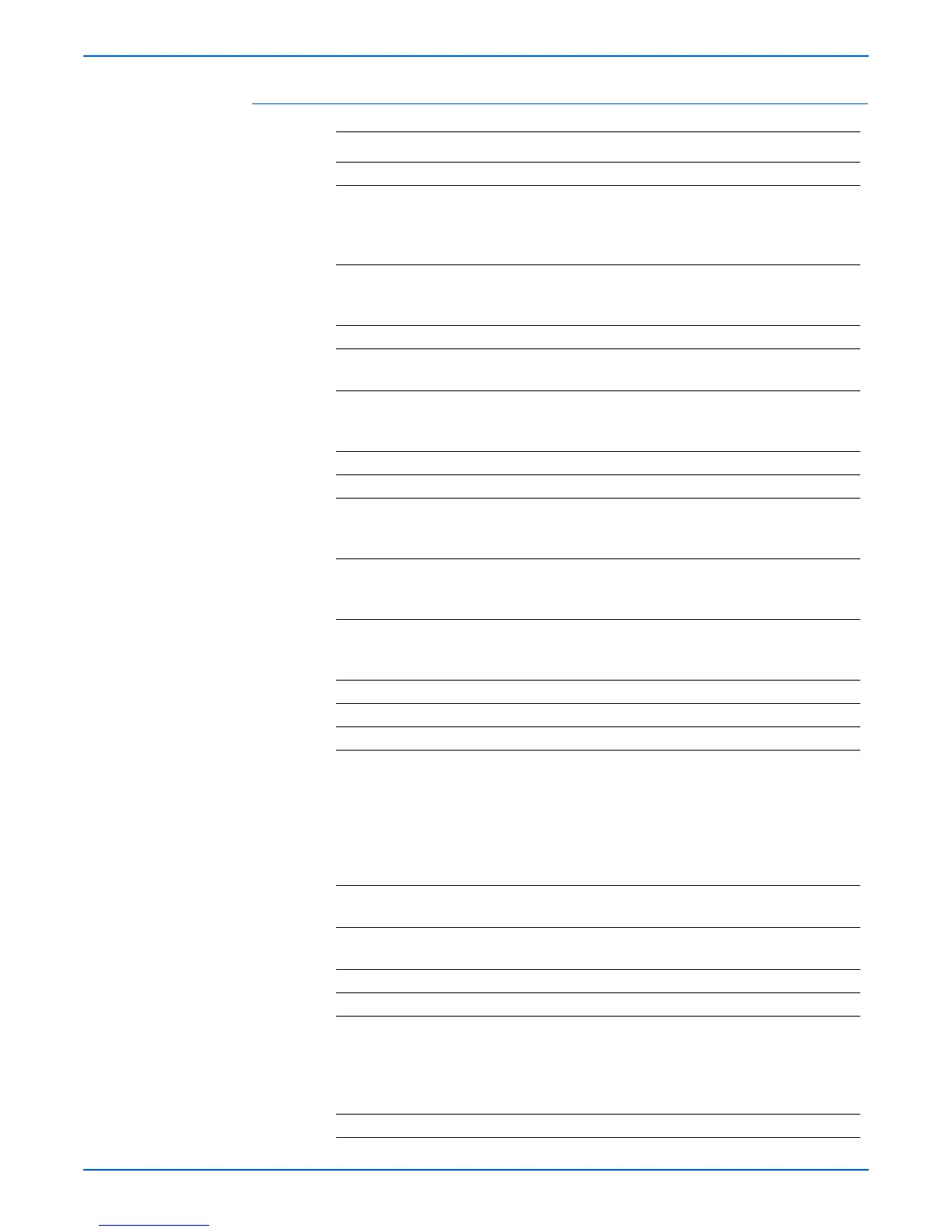

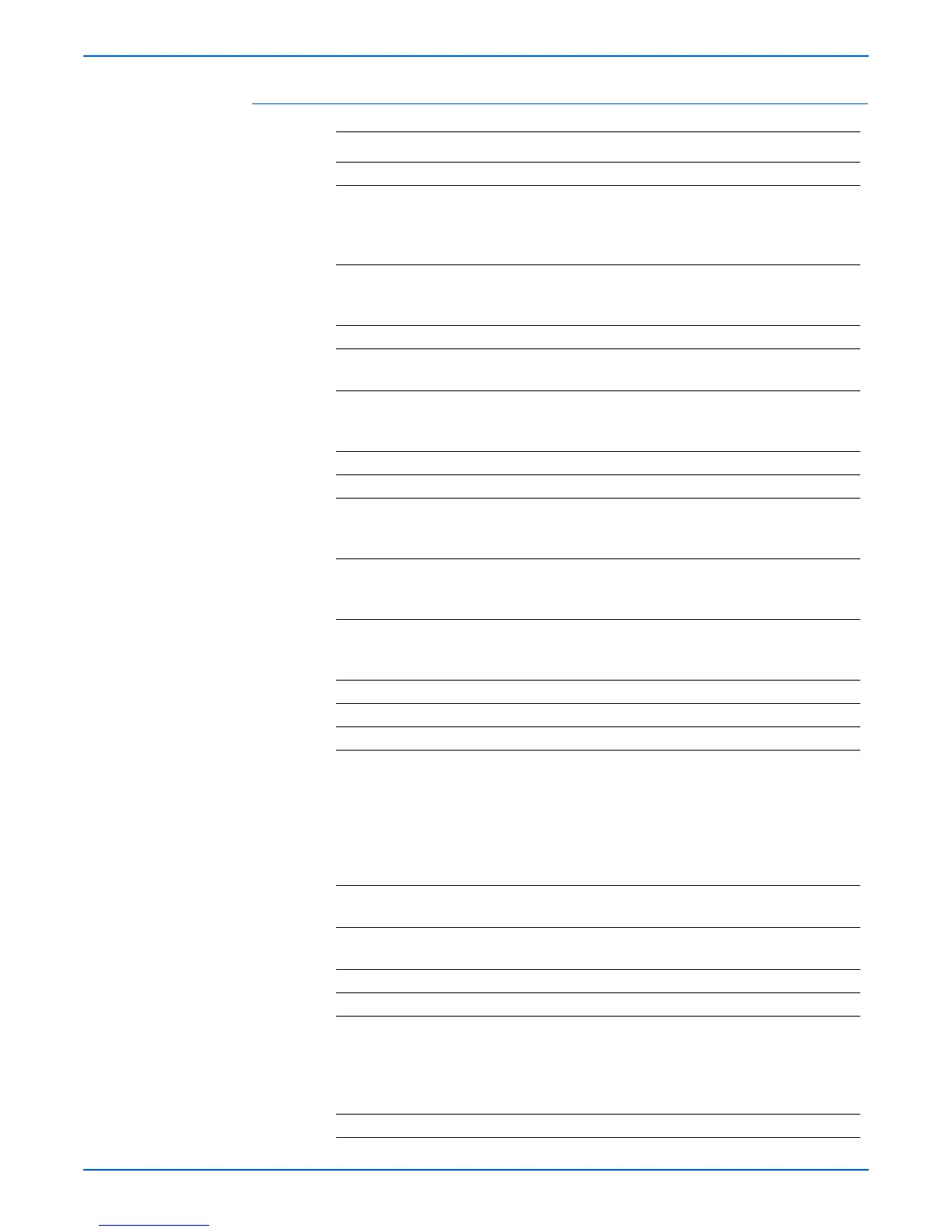

ASIC

Items Specification

Process 0.13 um (STDH150)

Package

■ 496 PBGA (total pad number: 597 ea)

■ Function pin: about 367pins

■ PWR & GND pin: 130 pins ((130/496) x 100 = 26.2%)

■ PWR & GND pad: 204 ea ((204/597) x 100 = 34.17%)

Voltage

■ Core Voltage: 1.2 V

■ I/O Pad Voltage: 3.3 V

■ RTC Voltage: 3 V

CPU Core ARM 920T (I-Cache: 16 KB, D-Cache-16 KB)

Operating Freq.

■ CPU Core: over 300 MHz

■ Target System Bus: 100 MHz

SDRAMC

■ 32 Bits Only, 100 MHz

■ 5 Banks (Up to 128 MB per Bank)

■ Feed-back clock (for SDRAM read) is appended

ROMC 4 Banks (Up to 16 MB per Bank)

IOC 6 Banks (Up to 16 MB per Bank)

DMAC 6 Channels (if CIP4e is not used, 4ch is available for external

DMA. If CIP4E is used (a4 DMA channel use), 2ch available

for external DMA)

HPVC

■ Dual/Single Beam

■ LVDS Pad (VDO, HSYNC)

■ Support A4 600 dpi, multi-pass color.

PVC

■ Dual/Single Beam

■ LVDS Pad (VDO, HSYNC)

■ Support A3 1200 dpi, multi-pass color.

UART 5 Channels (Channel 0 supports DMA/interrupt Operation)

INTERRUPT 6 External Interrupts, 26 Internal Interrupts

TIMER 6 System Timers

CIP4e

■ 300/400/600/1200 dpi CIS/CCD image sensor interface

■ Color/Mono grey image, Binary image scan support

■ 600 dpi Color/Mono Copy support

■ Image processing for High-End MFP, Digital Copier

■ MH/MR/MMR CODEC function for fax

■ Scan image: (max) A4 1200 dpi pixel processing

■ Copy image: (max) A4 600 dpi pixel processing

NAND Flash

Controller

■ 8/16 Bits, H/W ECC Generation

■ Auto Boot Mode (using internal SRAM, 4 KB)

MAC

■ 10M/100 Mbps

■ Full IEEE 802.3 compatibility

GEU Graphic Execution Unit

RSH Fully Hardware Rotator/Scaler/Halftoner support

Engine Controller

■ LSU Interface unit, contained APC function.

■ Step Motor: 4 Phase

■ PWM: 8 Channels

■ ADC: 8 Channels

■ BLDC clock support.

APC DAC (2 ea)

Loading...

Loading...