Virtex-5 RocketIO GTP Transceiver User Guide www.xilinx.com 145

UG196 (v1.3) May 25, 2007

Oversampling

R

Configuring the PCS Internal Datapath and Clocks

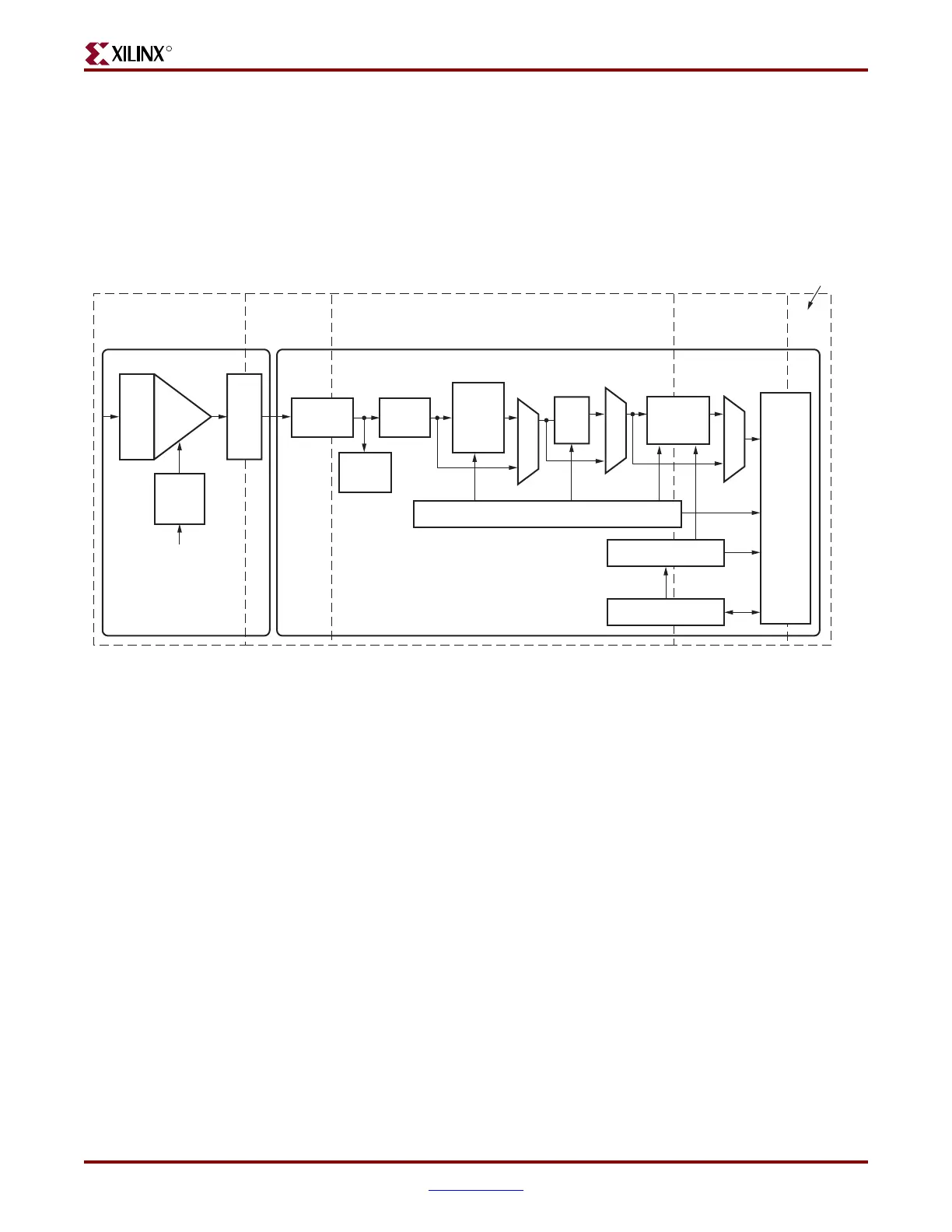

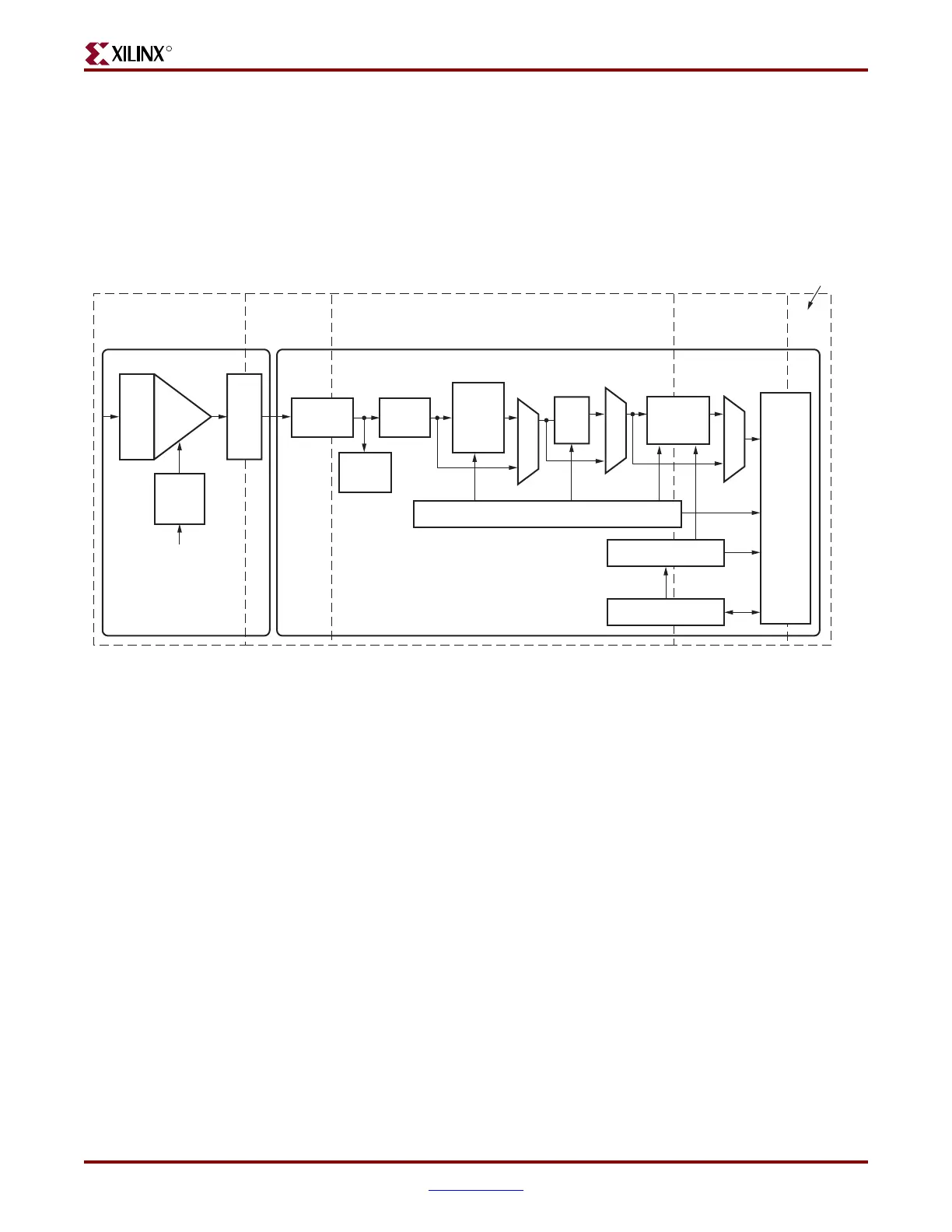

Figure 7-9 shows the clock domains of the GTP RX datapath when oversampling is used.

The RX serial clock runs at the PMA line rate calculated previously. The XCLK runs at the

resulting parallel rate for a 10-bit datapath, PMALineRate/10. The oversampled data from

the SIPO is fed into the oversampling block at the XCLK rate.

The oversampling block produces 2 bits of data for every 10 bits received. This data is fed

into the remaining PCS datapath at the required clock rate for the desired line rate, which

is given by Equation 7-5. This PCS rate is used for RXUSRCLK. A multiple of the rate is

used for RXUSRCLK2, depending on the selected RX datapath width.

When oversampling is used, the oversampled line rate, not the PMA line rate, and the PCS

internal datapath width, which is set by INTDATAWIDTH, must be used for RXUSRCLK

calculations. “FPGA RX Interface,” page 182 provides more details about the relationship

between RXUSRCLK and RXUSRCLK2.

Activating and Operating the Oversampling Block

After the PMA line rate and PCS datapath are set, the oversampling block can be enabled

by setting OVERSAMPLING_MODE to TRUE. This attribute affects both transceivers in

the GTP_DUAL tile.

The oversampling block includes a small buffer to hold data before passing it to the PCS.

This buffer can overflow/underflow if the PMA and PCS frequencies are different, such as

if RXUSRCLK stopped temporarily due to other events in the system. If an error in the

oversampling block buffer occurs, the transceiver asserts the RXOVERSAMPLEERR

signal. This error can be cleared by asserting RXRESET or RXCDRRESET.

RXENSAMPLEALIGN is tied High so the oversampling block always attempts to find the

best possible recovered clock and sample point in the incoming data.

Figure 7-9: RX Clock Domains When Using Built-In Oversampling

RX Serial Clock

RX-PMA RX-PCS

RX

CDR

PMA

PLL

Divider

From PMA PLL

RX

EQ

SIPO

10B

/

8B

PMA Parallel

Clock

(XCLK)

PCS Parallel

Clock

(RXUSRCLK)

Oversampling Block

Recovered Clock

(RXRECCLK)

RX Interface

Parallel Clock

(RXUSRCLK2)

Polarity

PRBS

Check

RX Pipe Control

FPGA

Logic

Comma

Detect

&

Align

UG196_c7_09_102306

RX Status Control

Loss of Sync

Elastic

Buffer

Over-

Sampling

Loading...

Loading...