190 www.xilinx.com Virtex-5 RocketIO GTP Transceiver User Guide

UG196 (v1.3) May 25, 2007

Chapter 8: Cyclic Redundancy Check (CRC)

R

The CRC Primitive

Each CRC block computes a 32-bit CRC using the CRC32 polynomial specified for PCI

Express, Gigabit Ethernet, and other common protocols. The CRC32 polynomial is:

Equation 8-1

There are two primitives for instantiating CRC integrated blocks. The 32-bit CRC primitive

(CRC32) can process 8, 16, 24, or 32-bit input data and generates a 32-bit CRC. The 64-bit

primitive (CRC64) can process 8, 16, 24, 32, 40, 56, or 64-bit input data and also generates a

32-bit CRC. Using the CRC64 primitive consumes both CRC integrated blocks paired with

a given transceiver tile.

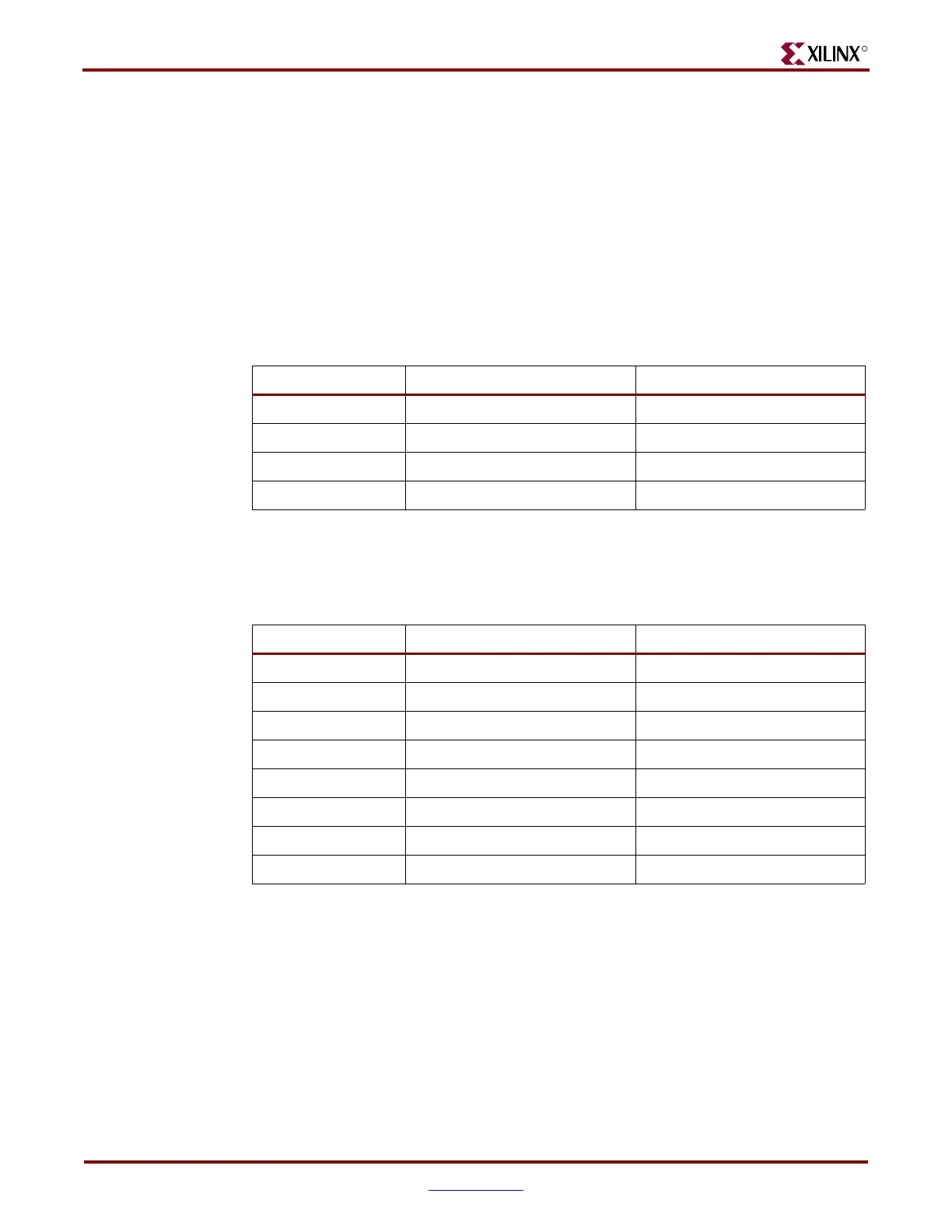

For CRC64, CRCDATAWIDTH is interpreted as indicated in Table 8-5.

GX() X

32

X

26

X

23

X

22

X

16

X

12

X

11

X

10

X

8

X

7

X

5

X

4

X

2

X 1++++++++++++++=

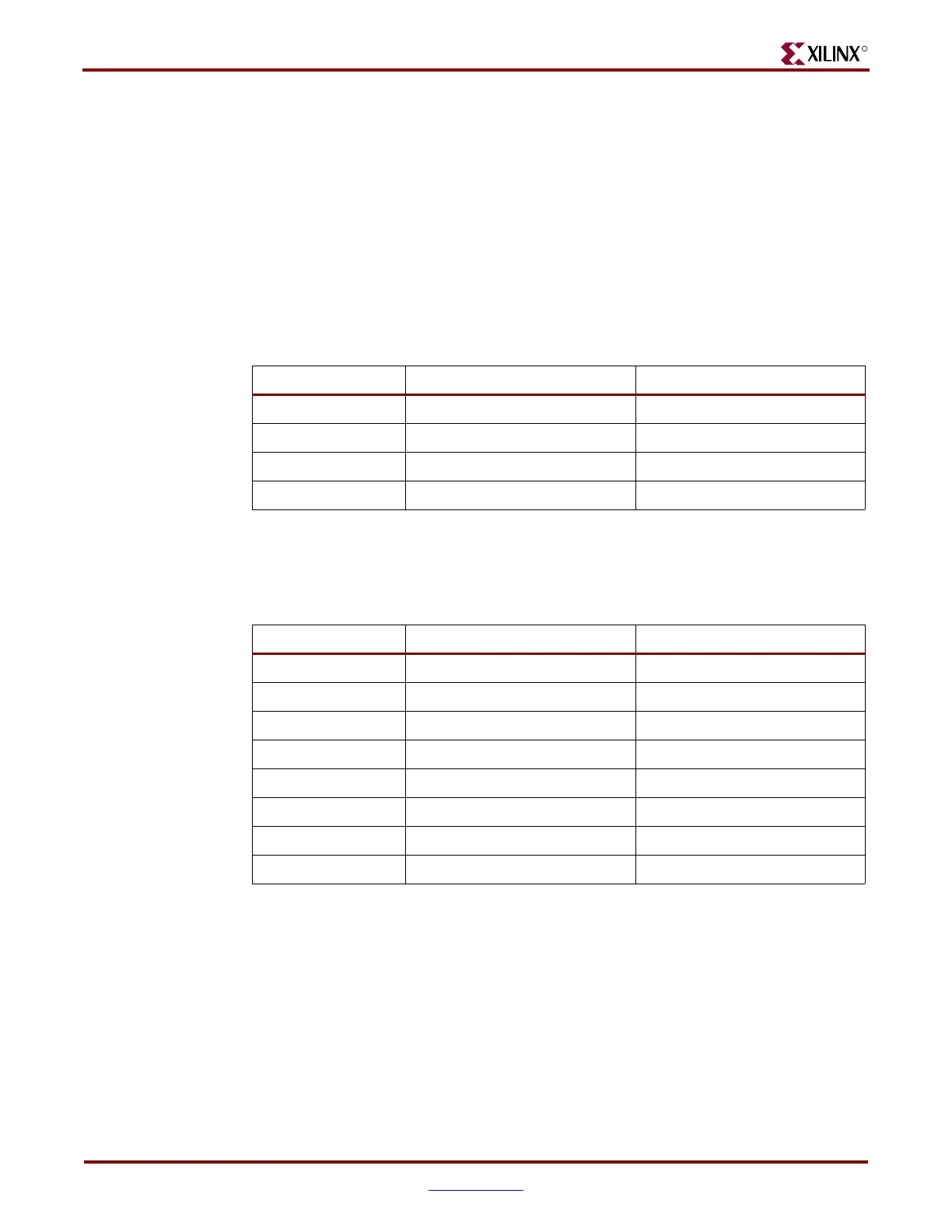

Table 8-4: CRC32 – Valid Data Widths

CRCDATAWIDTH[2:0] Data Width CRC Data Bus Bits

000 8-bit CRCIN[31:24]

001 16-bit CRCIN[31:16]

010 24-bit CRCIN[31:8]

011 32-bit CRCIN[31:0]

Notes:

1. CRCDATAWIDTH[2] must ALWAYS be set to 0 for the CRC32 primitive.

Table 8-5: CRC64 – Valid Data Widths

CRCDATAWIDTH[2:0] Data Width CRC Data Bus Bits

000 8-bit CRCIN[63:56]

001 16-bit CRCIN[63:48]

010 24-bit CRCIN[63:40]

011 32-bit CRCIN[63:32]

100 40-bit CRCIN[63:24]

101 48-bit CRCIN[63:16]

110 56-bit CRCIN[63:8]

111 64-bit CRCIN[63:0]

Loading...

Loading...